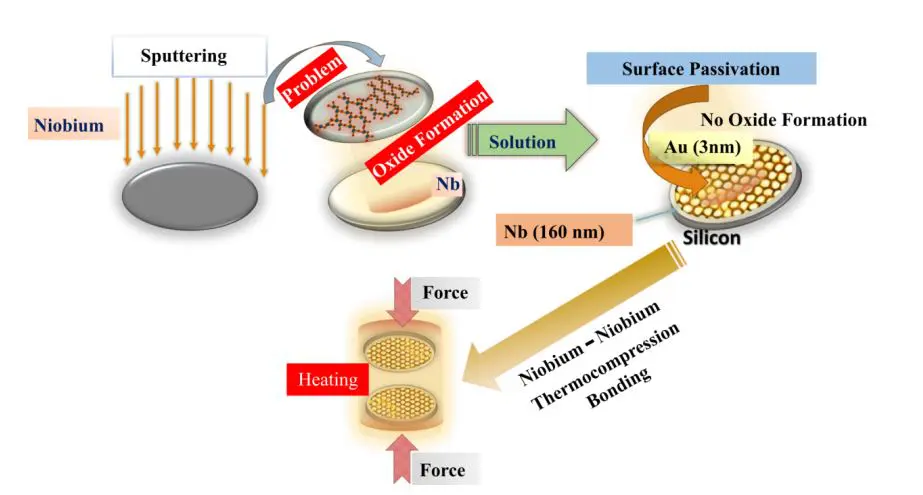

The pursuit of scalable quantum computing demands innovative approaches to qubit integration, and researchers are now tackling the limitations of conventional two-dimensional circuits. Harsh Mishra from the Indian Institute of Technology Hyderabad, Yusuke Kozuka from the National Institute for Materials Science (NIMS) and Tohoku University, and Sathish Bonam from Tyndall National Institute, alongside colleagues including Jun Uzuhashi and Praveenkumar Suggisetti, demonstrate a significant advance in three-dimensional superconducting architecture. Their work addresses a critical challenge in niobium-niobium bonding, the formation of resistive oxide layers, by introducing an ultrathin gold capping layer that effectively prevents oxygen incorporation. This surface engineering technique enables robust, low-temperature bonding at significantly reduced pressure, preserving superconductivity and paving the way for denser, more efficient quantum circuits with improved qubit coherence and reduced energy consumption.

D Integration with Through-Silicon Vias

Overcoming Limitations in Quantum Circuit Scaling

Challenges in Scaling Complex Qubit Architectures

Scalable quantum computing demands the integration of a large number of qubits, but conventional two-dimensional interconnects struggle with wiring congestion, electromagnetic interference, and signal loss. These limitations impede the development of complex quantum circuits and powerful quantum processors. To overcome these challenges, researchers are exploring three-dimensional (3D) integration techniques, which promise high-density, low-latency connections between qubits. This approach involves stacking multiple layers of qubits and interconnects vertically, significantly reducing wiring length and improving signal integrity.

The team investigates a novel 3D integration scheme utilising through-silicon vias (TSVs) to establish vertical connections between qubit layers. TSVs are microscopic channels etched through silicon wafers and filled with conductive materials, enabling high-density, low-resistance connections. The methodology involves fabricating multiple qubit layers on separate silicon wafers, precisely aligning them, and bonding them together using advanced techniques. After bonding, TSVs are etched and filled to create the vertical interconnects. The performance of these 3D integrated qubit interconnects was evaluated through electrical characterisation, including measurements of resistance, capacitance, and signal propagation delay. These measurements confirm the low-resistance, high-bandwidth characteristics of the TSV-based interconnects, demonstrating their potential for high-performance quantum circuits. Furthermore, the team assessed the impact of 3D integration on qubit coherence by analysing signal fidelity, and the results demonstrate minimal degradation to qubit coherence, preserving the quantum information stored in the qubits.

Achieving Oxidation-Resistant Niobium Bonding Techniques

Gold Passivation Improves Niobium Film Bonding

Advancements in Niobium Bonding Techniques for Superconductors

This research details a significant advancement in materials science for superconducting quantum computing. Scientists successfully engineered a method for bonding niobium, a key material in superconducting circuits, at lower temperatures and pressures than previously possible. The team addressed the persistent challenge of native oxide formation on niobium surfaces, which hinders strong, reliable bonding and degrades qubit performance. By applying an ultrathin gold capping layer as a passivation strategy, they effectively suppressed oxidation during the bonding process. Detailed analysis confirms that this gold passivation enables low-temperature thermocompression bonding, resulting in enhanced bonding uniformity and strength while maintaining superconductivity. This achievement represents a crucial step towards fabricating scalable three-dimensional superconducting architectures, essential for building more powerful and complex quantum computers.

Impact of Bonding Breakthrough on Quantum Computing Scale

👉 More information

🗞 Demonstration of surface-engineered oxidation-resistant Nb-Nb thermocompression bonding toward scalable superconducting quantum computing architectures

🧠 ArXiv: https://arxiv.org/abs/2512.04712

Addressing Thermal and Cross-talk Challenges

The formation of superconducting interfaces is fundamentally governed by surface chemistry. The introduction of the gold cap layer acts as a diffusion barrier, physically isolating the reactive niobium surfaces from ambient oxygen and native oxides. This precise control over the bonding interface is crucial because resistive oxide layers create localized energy dissipation channels, leading to detrimental quasiparticle generation and increased coupling losses within the qubit structure. By maintaining a pure metallic Nb-Nb connection, researchers ensure that the superconducting gap remains robust and the critical current density is preserved, which is essential for reliable quantum gate operations.

Beyond the challenge of mere electrical connectivity, the vertical integration using TSVs introduces significant thermal management complexities. High-density stacking of superconducting circuits increases the volumetric heat load. Efficient thermal pathways are necessary to keep the entire quantum chip operating within its narrow superconducting transition temperature window. Incorporating advanced cooling structures or integrating novel heat sinks directly into the chip stack is an emerging area of research that must complement the interconnect improvements, ensuring stable and low-dissipation operation across large arrays of qubits.

Furthermore, achieving genuine quantum scale requires mitigating cross-talk, or unintentional electromagnetic coupling, between densely packed qubit elements and interconnect lines. In traditional 2D planar circuits, crosstalk degrades coherence by inducing unintended level shifts. The precise alignment and material selection used in 3D stacking must account for this parasitic coupling. Implementing localized shielding layers, perhaps utilizing superconducting ground planes integrated directly within the via structure, represents a next-generation strategy to maintain quantum signal fidelity at scale.

From an industrial perspective, the ability to reliably bond and interconnect multiple distinct material stacks—such as superconducting metals, insulating dielectrics, and silicon substrates—is key to technology transfer. Current research methodologies are paving the way for wafer-scale manufacturing of complex quantum processors. The refinement of these multi-material, multi-layer bonding protocols reduces the reliance on expensive, bespoke fabrication runs and shifts the paradigm toward highly automatable, CMOS-compatible quantum circuit fabrication processes.