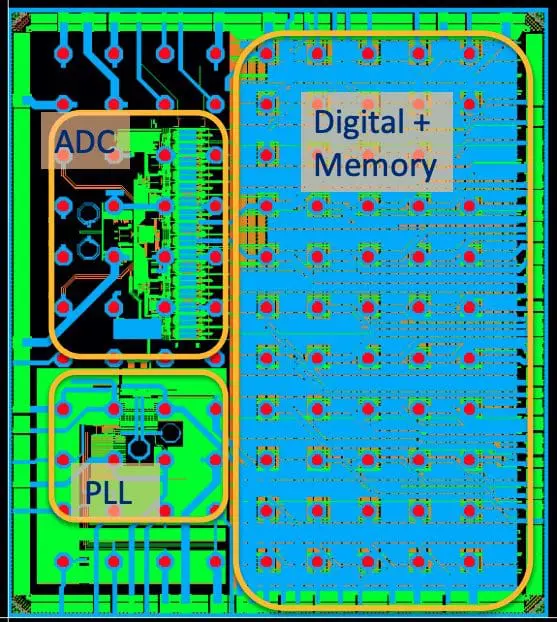

Researchers from Fermi National Accelerator Laboratory and Microsoft Quantum are developing a 12-bit 10GSPS Cryogenic ADC for Quantum Readout. The project aims to improve the testing of qubit devices, reduce connections between the cryogenic plane and room temperature, and lower the control loop latency for error correction algorithms. The team focuses on multiplexing and data conversion, using the process technology node GF 22FDX for its excellent cryogenic performance. The project, known as ROADS, is a significant advancement in quantum computing, with goals including testing custom capacitor mismatch and redesigning the PLL using a sampled architecture.

What is the Design of a 12bit 10GSPS Cryogenic ADC for Quantum Readout?

The design of a 12-bit 10GSPS Cryogenic ADC for Quantum Readout is a project undertaken by a team of researchers from Fermi National Accelerator Laboratory and Microsoft Quantum. The project aims to develop a large-scale system for high-throughput testing of qubit devices. This system is designed to drastically reduce the connections between the cryogenic plane and room temperature, lower the latency of the control loop for implementing error correction algorithms, and provide invaluable statistical insight into material properties. The project is primarily focused on innovating the multiplexing and data conversion.

How Does the Control and Readout Interface to Qubits Work?

The control and readout interface to qubits is a complex process with ample room for improvement. One popular readout scheme is combining RF reflectometry with frequency domain multiplexing. In this approach, many qubits share a single RF transmission line. Each qubit is tuned to have a unique resonate frequency such that they can be read out in parallel. The project is working towards direct-to-digital, which requires wide bandwidth and high linearity. Such an ADC is required to be state-of-the-art and is the specific focus of the project.

What is the Choice of Process Technology Node GF 22FDX?

The choice of process technology node GF 22FDX is a multi-technology platform that offers excellent cryogenic performance. It includes FETs 0.8 V transistors with additional back gate control, EGFETs 1.8 V transistors with additional back gate control, and good metal stacks and pcell options for inductors. The platform also offers high-density memory SRAMs 0.5 V option, eMRAMs, and digital power supply scaling 0.8 V below 400 mV ULP ultra-low power performance. The team is also investigating photonic integration high-speed data transfer from RT to cryo.

What are the ADC Requirements in RF Reflectometry?

The ADC dynamic range spec is determined by the number of tones, the full path response from all components before the ADC, and the noise requirements. The ADC sample rate spec is determined by the required bandwidth, the number of tones, tone separation, RF photon energy limits, and the importance of the PLL. The project aims to meet these specifications by designing many circuit blocks with very demanding specifications. All blocks were designed from scratch, which was time-intensive.

What is the ROADS Timeline and Goals?

The ROADS project has a timeline and set of goals that include the testing of custom capacitor mismatch, the creation of four separate subADCs, and the full initial iteration of high-performance PLL. The project also aims to redesign the PLL using a sampled architecture and final tuning of designs to meet state-of-the-art specifications. The project is a significant step forward in the field of quantum computing, offering potential improvements in control and readout, multiplexing and data conversion, and process technology.

Publication Date: 2024-02-14

Authors: D. Braga, Kushal Das, Neil Dick, Ken Dyer et al.

Source:

DOI: https://doi.org/10.2172/2305625