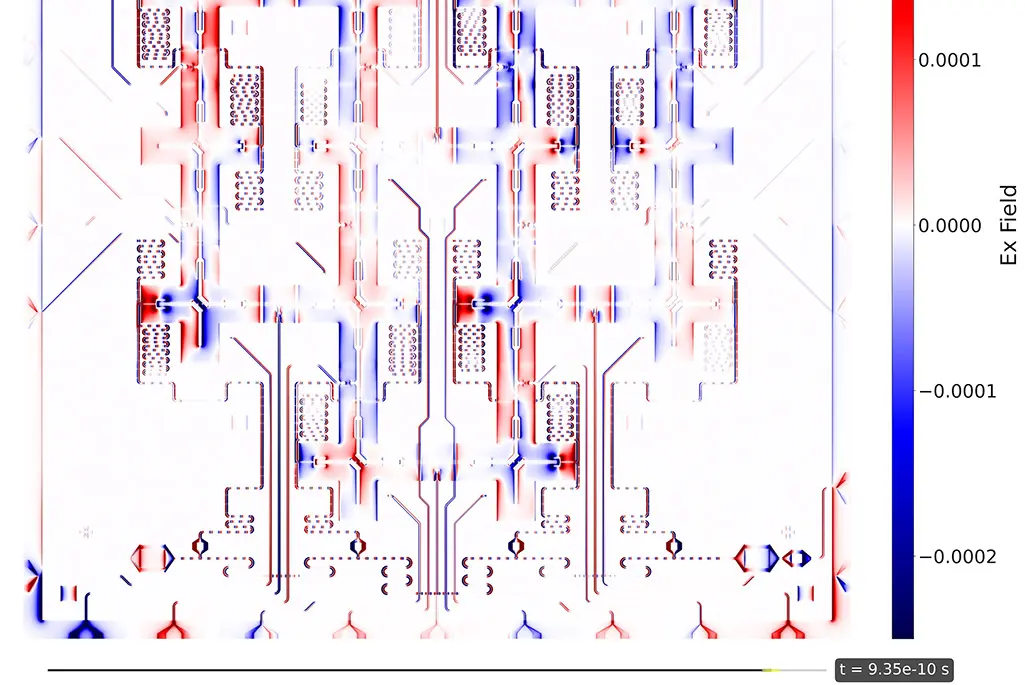

Zhi Jackie Yao and Andy Nonaka of the Applied Mathematics and Computational Research (AMCR) Division at Lawrence Berkeley National Laboratory, in collaboration with Irfan Siddiqi’s Quantum Nanoelectronics Laboratory at the University of California, Berkeley, have completed an unprecedented simulation of a 10mm² quantum microchip using 7,168 NVIDIA GPUs on the Perlmutter supercomputer at the National Energy Research Scientific Computing Center (NERSC). Employing their exascale modeling tool, ARTEMIS, the researchers discretized the 0.3mm-thick chip into 11 billion grid cells to predict electromagnetic wave propagation and optimize signal coupling. This work, to be demonstrated at SC25, represents a critical advancement in accelerating the design and development of high-performance quantum hardware.\n\n

Simulating Quantum Chip Performance with Exascale Computing

\n\nResearchers at Berkeley Lab and UC Berkeley achieved a breakthrough in quantum chip design by completing an unprecedented simulation using the Perlmutter supercomputer. Leveraging 7,168 NVIDIA GPUs, they modeled a 10mm x 0.3mm chip with micron-scale details – discretizing it into 11 billion grid cells. This full-wave, physical-level simulation, powered by the ARTEMIS tool, allows for detailed analysis of electromagnetic wave propagation, crucial for optimizing signal coupling and minimizing crosstalk within the complex quantum circuitry.\n\nThis simulation isn’t just about scale; it’s about fidelity. Unlike “black box” models, ARTEMIS incorporates material properties, layout, and wiring details, mimicking real-world experimental conditions. The team ran over a million time steps in seven hours, evaluating three circuit configurations daily – a feat impossible without Perlmutter’s exascale capabilities. This detailed approach allows researchers to understand how the chip functions internally, not just if it works, paving the way for improved designs.\n\nThe ultimate goal is to bridge the gap between simulation and fabrication. Researchers will soon compare these results with a physically built chip, refining the model for even greater accuracy. This work, supported by NERSC and the DOE’s Exascale Computing Project, highlights the power of large-scale computing in accelerating quantum technology. Strong collaboration between Berkeley Lab divisions and UC Berkeley was key to this successful undertaking, promising to unlock new capabilities in quantum research.\n\n

Detailed Modeling Captures Chip-Level Physicality

\n\nResearchers have achieved an unprecedented simulation of a quantum microchip, leveraging the power of the Perlmutter supercomputer with 7,000 NVIDIA GPUs. This detailed modeling—discretizing the 10mm x 0.3mm chip into 11 billion grid cells—goes beyond treating the chip as a “black box.” Instead, it meticulously accounts for material properties, layout, and wiring – even down to micron-scale etchings – offering a full-wave, physical-level simulation crucial for optimizing quantum circuit design and minimizing signal interference.\n\nThis level of fidelity required substantial computing power, running over a million time steps in just seven hours. The simulation uses ARTEMIS, a tool developed under the DOE’s Exascale Computing Project, to solve Maxwell’s equations in the time domain, capturing nonlinear behavior and accurately modeling qubit interactions. This approach allows researchers to predict the chip’s performance before fabrication, identifying potential issues and accelerating the development cycle for increasingly complex quantum hardware.\n\nThe impact extends beyond simply validating designs. By mimicking experimental conditions, the simulation provides a quantitative understanding of spectral behavior and resonance, enabling researchers to benchmark against physical experiments. This powerful combination of detailed modeling and real-time simulation—supported by a collaborative effort across Berkeley Lab, UC Berkeley, and NERSC—represents a critical step towards building more powerful and performant quantum chips and unlocking new scientific discoveries.\n\n

Massively Parallel Simulation Enables Unprecedented Resolution

\n\nResearchers achieved an unprecedented simulation of a quantum microchip using 7,000 NVIDIA GPUs on the Perlmutter supercomputer. This wasn’t just about scale; the simulation discretized the 10mm x 0.3mm chip into 11 billion grid cells, enabling a full-wave, physical-level model. This level of detail—accounting for material properties, layout, and wiring—moves beyond treating chips as “black boxes” and allows for predicting performance before fabrication, significantly accelerating quantum hardware development.\n\nThis massive simulation ran over a million time steps in just seven hours, evaluating three circuit configurations daily—a feat impossible without Perlmutter’s full processing power. Crucially, the model isn’t static; it simulates chip behavior in the time domain using Maxwell’s equations, capturing nonlinear effects and mirroring real-world experimental conditions. This allows researchers to understand how qubits communicate and interact within the circuit, offering insights beyond simple functional testing.\n\nThe simulation’s ultimate test will be validation against a physically fabricated chip. However, this detailed modeling represents a critical step toward building more powerful and performant quantum computers. The collaboration between Berkeley Lab’s various divisions, alongside NERSC’s computing resources, demonstrates the power of interdisciplinary partnerships in pushing the boundaries of quantum technology and unlocking new scientific avenues.\n\n

Collaborative Effort Advances Quantum Hardware Design

\n\nResearchers at Lawrence Berkeley National Laboratory and UC Berkeley achieved a breakthrough in quantum hardware design through an unprecedented simulation. Utilizing 7,000 NVIDIA GPUs on the Perlmutter supercomputer, they modeled a 10mm x 0.3mm quantum chip with features down to one micron in width. This detailed simulation, discretizing the chip into 11 billion grid cells, allows for predictive analysis of chip performance before fabrication, optimizing designs and minimizing potential issues—a crucial step towards scalable quantum computing.\n\nThis wasn’t a simplified “black box” simulation. The team employed ARTEMIS, a full-wave electromagnetic modeling tool, to simulate the chip’s physical properties – materials, layout, wiring – and its behavior in the time domain. This captures nonlinear effects and mimics real-world experimental conditions, allowing researchers to observe qubit communication and resonance within the circuit. Running over a million time steps in just seven hours showcases Perlmutter’s power for complex quantum system modeling.\n\nThe simulation represents a significant advancement because of the scale and fidelity. By meticulously modeling a physically realistic chip, the team aims to quantitatively validate the design before physical fabrication. This collaborative effort, leveraging expertise from Berkeley Lab, UC Berkeley, and NERSC, unlocks new capabilities for quantum hardware development and promises to accelerate progress towards more powerful and performant quantum computers for scientific discovery.\n\n