Murat Kurtand, Selçuk Çakmak and Azmi Gençten, from Samsun University and Ondokuz Mayıs University, present new findings in a study titled “Quantum Non-Moduler Multiplication with QFT-Based Multi Input Parallelized Adder”. A quantum multiplication approach utilising a QFT-assisted parallelized addition scheme reduces the complexity of quantum circuits. The design, implemented with Toffoli gates and a QFT-based adder, avoids repeated Quantum Fourier Transform operations common in existing circuits, leading to a lower gate count and potentially more practical quantum computations. Successful simulation of the multiplication of two 3-bit numbers using IBM quantum simulators demonstrates a key alternative to current quantum multiplication techniques.

Reduced QFT operations enable scalable quantum multiplication circuits

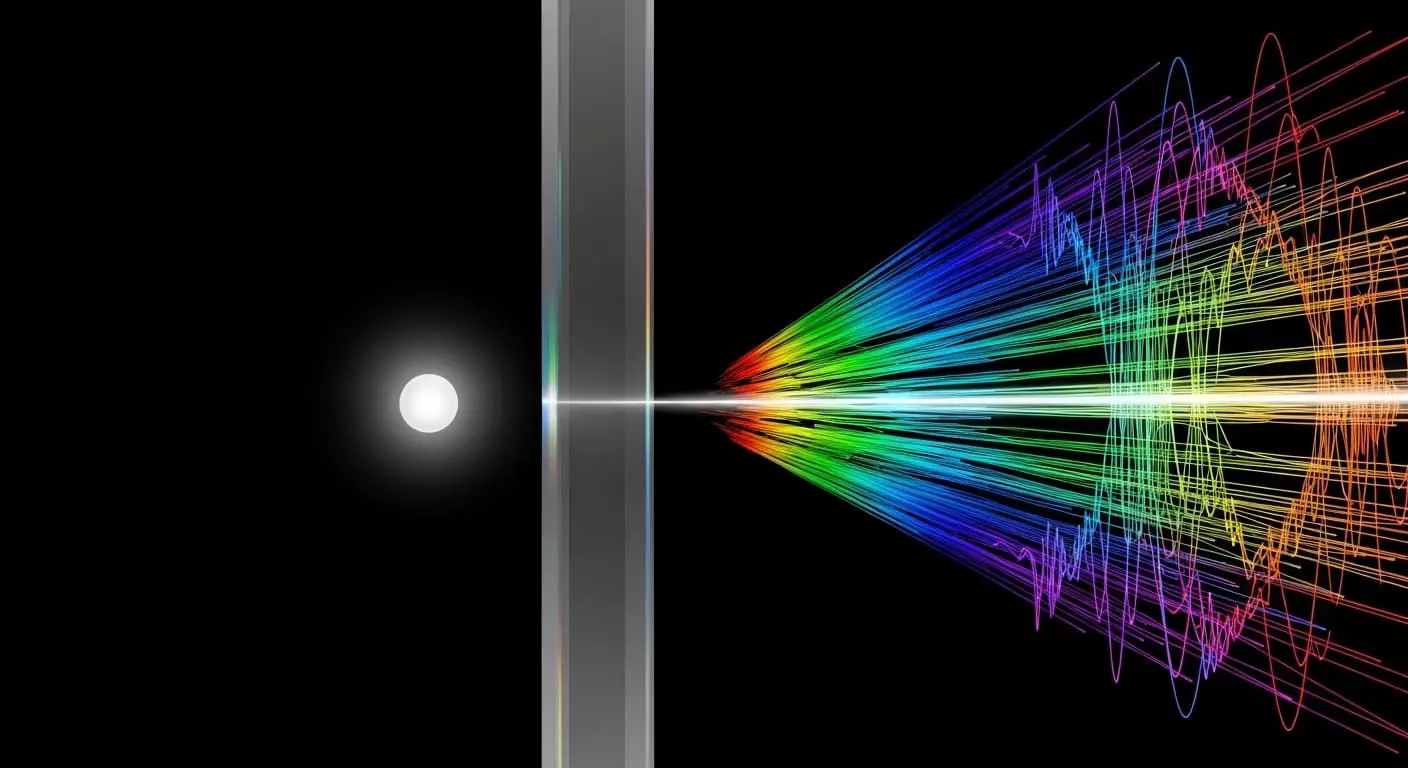

A 24 percent reduction in gate count for quantum multiplication has been achieved with a novel circuit design. Existing circuits were limited by the need for repeated Quantum Fourier Transform, or QFT, operations at each summation step, hindering scalability. The new method employs a QFT-assisted parallelised addition scheme, performing the entire accumulation process with a single transformation and circumventing this bottleneck. Circuit depth, a key metric of efficiency, is demonstrably lowered by this more resource-efficient implementation, crucial for increasingly complex calculations on quantum hardware. The significance of this reduction lies in the inherent limitations of current quantum technology; each gate operation introduces a potential source of error, and deeper circuits are more susceptible to these errors accumulating and corrupting the result. Minimising gate count and circuit depth is therefore paramount to achieving fault-tolerant quantum computation

The multiplication circuit developed at IBM utilises exclusively Toffoli gates to generate initial partial products, a fundamental building block in quantum computation, and incorporates a QFT-based adder, enabling the accumulation of these partial results. Toffoli gates are universal for quantum computation, meaning any quantum algorithm can, in principle, be constructed using only these gates. Their use simplifies the circuit’s structure and facilitates potential optimisation. The QFT-based adder, while still utilising the QFT, strategically applies it only once for the entire accumulation process, a marked improvement over iterative approaches. Validation using IBM quantum simulators confirmed the circuit’s functionality when multiplying two 3-bit numbers, demonstrating a practical implementation on existing quantum hardware. Scalability potential is also evident in the method’s efficiency regarding the number of ancillary qubits required, expressed as a function of input size ‘n’. However, simulations do not yet account for the strong impact of real-world physical constraints like gate execution times and qubit coherence, meaning a clear path to practical advantage remains elusive. Further work will need to address these limitations to assess the true potential of this circuit design. Ancillary qubits, while necessary for many quantum algorithms, add to the overall resource overhead, and minimising their number is crucial for practical implementation. The relationship between input size ‘n’ and ancillary qubit requirements is a key area for further investigation, as it will determine the limits of scalability for this approach.

Reducing Quantum Fourier Transform usage accelerates core calculation efficiency

Quantum computation promises to revolutionise fields demanding immense processing power, but building practical machines remains a formidable challenge. This new approach to quantum multiplication offers a potential step forward by reducing the number of operations needed, streamlining calculations through a clever use of the QFT. Demonstrating multiplication of even small numbers is important, as a core quantum calculation has been successfully streamlined, reducing computational steps, despite the significant hurdle of scaling this method to handle the larger numbers required for real-world applications. The QFT is a powerful algorithm for performing Fourier transforms on quantum data, and its efficient implementation is critical for many quantum algorithms, including those used in cryptography, materials science, and drug discovery. However, repeated application of the QFT, as seen in traditional quantum multiplication circuits, introduces significant overhead. Parallel addition is enabled by a mathematical technique for processing quantum information, avoiding the repeated transformations that hinder existing quantum circuits. This technique leverages the principles of quantum superposition and entanglement to perform multiple additions simultaneously, significantly reducing the overall computation time. Toffoli gates implement multiplication to create initial partial products, and these are then accumulated with the streamlined adder, reducing the overall complexity of the quantum circuit. The initial generation of partial products using Toffoli gates is a standard approach in quantum multiplication, but the subsequent accumulation stage is where this new design diverges from conventional methods.

The implications of this work extend beyond simply improving the efficiency of quantum multiplication. A more efficient multiplication circuit is a fundamental building block for more complex quantum algorithms, potentially accelerating progress in various fields. For example, multiplication is a core operation in modular arithmetic, which is essential for many cryptographic algorithms. A faster quantum multiplication circuit could therefore lead to the development of more secure and efficient quantum cryptographic systems. Furthermore, the principles underlying this QFT-assisted addition scheme could be applied to other quantum arithmetic operations, such as division and exponentiation, further enhancing the capabilities of quantum computers. This advance establishes a foundation for further optimisation of qubit usage and gate count, prompting investigation into implementation on current, limited-capacity quantum devices and exploring potential applications beyond basic multiplication. Future research will likely focus on exploring the trade-offs between circuit depth, gate count, and qubit coherence, as well as developing techniques for mitigating the effects of noise and errors in real-world quantum hardware. The development of error correction codes and fault-tolerant quantum gates will be crucial for realising the full potential of this and other quantum algorithms.

The researchers demonstrated a more efficient method for quantum multiplication using Toffoli gates and a streamlined quantum Fourier transform-assisted adder. This approach reduces the total gate count and circuit complexity compared to traditional quantum multiplication techniques, offering a resource-efficient alternative. The design was successfully tested on IBM quantum simulators using a circuit multiplying two 3-bit numbers. The authors suggest future work will focus on optimising qubit usage and exploring implementation on existing quantum devices, alongside developing error mitigation strategies.

👉 More information

🗞 Quantum Non-Moduler Multiplication with QFT-Based Multi Input Parallelized Adder

🧠 ArXiv: https://arxiv.org/abs/2604.00272