The efficient execution of quantum algorithms on current quantum hardware necessitates the translation of abstract quantum circuits into a form compatible with the physical constraints of quantum processing units (QPUs). This ‘transpilation’ process introduces significant overhead, particularly in terms of gate count and circuit depth, which directly impacts fidelity on noisy intermediate-scale quantum (NISQ) devices. Researchers from the Jülich Supercomputing Centre, Virginia Tech, and Purdue University, led by J. A. Monta˜nez-Barrera, Yanjun Ji, Michael R. von Spakovsky, David E. Bernal Neira, and Kristel Michielsen, detail a novel approach to optimising this transpilation for the quantum approximate optimisation algorithm (QAOA). Their work, entitled ‘Optimizing QAOA circuit transpilation with parity twine and SWAP network encodings’, introduces a simulated annealing-based method that demonstrably reduces both the number of two-qubit gates and the overall circuit depth required to implement QAOA circuits, exceeding the performance of standard transpilation techniques, and extending viable circuit sizes on real hardware.

Current quantum processing units (QPUs) present significant challenges for implementing complex quantum algorithms. A primary limitation is the fixed connectivity of qubits – not every qubit can directly interact with every other. This necessitates transpilation, the process of transforming a logical quantum circuit into a physical one executable on the hardware, often requiring the insertion of additional gates to facilitate qubit interactions. Researchers are actively developing techniques to minimise the resources – gate count and circuit depth – required by this transpilation process.

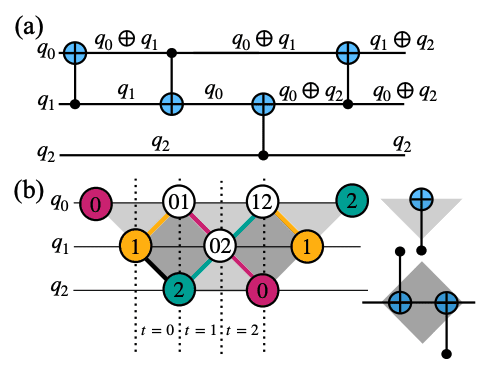

This work introduces a simulated annealing-based method designed to reduce the demand for both parity twine chains (PTC) and SWAP networks when encoding quantum approximate optimisation algorithm (QAOA) circuits onto QPUs with limited connectivity. PTC encoding represents a technique for establishing connectivity between qubits using a specific arrangement of gates, while SWAP networks involve a series of SWAP gates to move quantum information between non-adjacent qubits. Reducing the need for both these elements improves resource efficiency and enables the execution of more complex computations.

The core of this research lies in a

The core of this research lies in a simulated annealing algorithm that intelligently maps qubits, minimising the number of two-qubit gates required to represent a given quantum circuit. Simulated annealing mimics the process of slowly cooling a material to reach a low-energy state; in this context, it translates to a circuit with minimal gate count and depth. The algorithm systematically explores different qubit mappings, accepting improvements that reduce circuit complexity while occasionally accepting worse solutions to avoid becoming trapped in suboptimal configurations.

Benchmarking against conventional transpilers revealed substantial improvements, particularly for circuits with limited connectivity. For a 120-qubit instance with 25% connectivity, the method achieved an 85% reduction in circuit depth and a 28% reduction in the number of two-qubit gates. This allows for the execution of more complex algorithms on near-term quantum hardware.

Critically, the benefits of this approach were validated on actual hardware. Running a QAOA instance on IBM’s ‘ibm_fez’ quantum computer demonstrated improved performance up to 20 qubits, exceeding the 15-qubit limit previously achievable with SWAP networks alone. This practical validation underscores the importance of considering both algorithmic optimisation and hardware constraints when designing quantum computations.

The focus on PTC encoding, combined with the simulated annealing optimisation, represents a promising step towards overcoming connectivity limitations and unlocking the full potential of quantum algorithms. Minimising the number of two-qubit gates reduces the probability of errors and improves the reliability of results.

Researchers validated the practical impact of PTC encoding

Researchers validated the practical impact of PTC encoding by benchmarking QAOA on the ibm_fez device, observing improved performance up to 20 qubits compared to the 15-qubit limit achieved with SWAP networks, demonstrating the potential for scaling up quantum computations and tackling more complex problems.

Ongoing research focuses on further improving the performance of the simulated annealing algorithm and optimising encoding strategies, alongside the development of new error mitigation techniques to reduce the impact of noise and improve the reliability of quantum computations.

🗞 Optimizing QAOA circuit transpilation with parity twine and SWAP network encodings

🧠 DOI: https://doi.org/10.48550/arXiv.2505.17944