Microsoft has unveiled its Majorana 1 chip. It is a semiconductor-based device that leverages topological qubits. This marks a fundamental shift in the race for scalable quantum computing. This development underscores Microsoft’s commitment to a hardware architecture. This approach is distinct from conventional superconducting qubits. The latter is the dominant paradigm of firms like Google and IBM. Superconducting circuits have made significant strides in fault-tolerant computing. However, Microsoft’s topological approach promises intrinsic error resistance. This could potentially circumvent one of quantum computing’s most significant hurdles.

The Promise of Topological Qubits

Microsoft’s quantum strategy centers on the Majorana zero mode. It is an exotic quasiparticle theorized to exhibit non-Abelian anyonic behavior. First proposed by Ettore Majorana in 1937, these particles have the peculiar property of storing quantum information. This information is stored in a highly delocalized manner. This makes them inherently resistant to certain types of noise. By integrating these quasiparticles into the Majorana-1 chip, Microsoft aims to construct topological qubits. These qubits could achieve lower error rates than standard superconducting qubits.

Unlike traditional superconducting qubits, which require extensive error correction overhead to mitigate decoherence, topological qubits theoretically encode quantum states in a way that naturally reduces error susceptibility. If realized, this could drastically reduce the number of physical qubits required for fault-tolerant computation—a fundamental bottleneck in quantum scalability.

A Divergent Strategy in the Quantum Race

Microsoft’s pursuit of topological quantum computing diverges significantly from the prevailing strategies adopted by Google, IBM, and other quantum hardware players. Most major quantum efforts today rely on superconducting transmon qubits or trapped ion architectures, necessitating extensive error correction schemes to maintain computational integrity.

Google’s Sycamore processor demonstrated so-called quantum supremacy in 2019, and IBM’s Condor, a 1,121-qubit chip unveiled in 2023, exemplifies the superconducting approach. These qubits, while already functioning in noisy intermediate-scale quantum (NISQ) systems, face exponential resource requirements as they scale toward fault-tolerant regimes. In contrast, Microsoft’s Majorana-based qubits embodied into Majorana 1 seek to bypass this scaling issue by reducing intrinsic error rates at the hardware level rather than relying solely on software-driven error correction.

“It’s complex in that we had to show a new state of matter to get there, but after that, it’s fairly simple. It tiles out. You have this much simpler architecture that promises a much faster path to scale,”

Krysta Svore, Microsoft technical fellow.

Nonetheless, the feasibility of Microsoft’s approach remains an open question. Despite the theoretical promise, Majorana zero modes have been challenging to realize experimentally. Recent breakthroughs, including Microsoft’s 2022 experimental evidence of topological states in nanowires, suggest progress, but full-scale qubit implementation is still in its infancy.

Implications for the Future of Quantum Computing

If Microsoft’s Majorana 1 chip succeeds in demonstrating practical topological qubits, it could redefine the roadmap for fault-tolerant quantum computing. By minimizing the overhead required for quantum error correction, this approach could dramatically alter the economic and technical feasibility of quantum advantage in areas such as materials simulation, cryptography, and optimization problems.

However, while the Majorana 1 chip represents a significant milestone, several hurdles remain. Microsoft must demonstrate the stable, reproducible generation of topological qubits, validate their computational fidelity, and integrate them into a scalable quantum architecture. The next few years will determine whether this unconventional approach can match—or surpass—the rapid progress seen in superconducting qubit platforms.

With global investment in quantum computing reaching unprecedented levels, Microsoft’s Majorana 1 chip is a bold bet on an alternative path to scalable quantum advantage. If successful, it could challenge prevailing assumptions about the best route to practical quantum computing, potentially leapfrogging the limitations that have constrained existing qubit technologies.

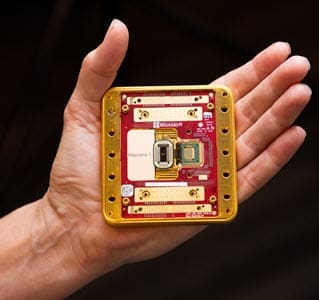

The conducting wire in quantum computers, known as qubits, can be controlled digitally using voltage pulses, simplifying the quantum computing process and reducing the physical requirements for building a scalable machine. This is one of the advantages of Microsoft’s topological qubit, which is small enough to fit into a hand but powerful enough to be integrated into a quantum computer that can be deployed inside Azure data centers.

The topological qubit architecture of Microsoft’s Majorana 1 chip consists of aluminum nanowires arranged in the shape of an H, each containing four controllable Majoranas and making one qubit. These Hs can be connected to form a larger structure, promising a more straightforward and faster path to scale.

“We are literally spraying atom by atom. Those materials have to line up perfectly. If there are too many defects in the material stack, it just kills your qubit,”

Krysta Svore, Microsoft technical fellow.

The quantum chip is part of an ecosystem. This ecosystem includes control logic and a dilution refrigerator for maintaining extremely low temperatures. It also has a software stack that integrates with AI and classical computers. While years of engineering work continue to refine these processes and get all the elements to work together at an accelerated scale, Microsoft said many difficult scientific and engineering challenges have now been met.

One of the most challenging aspects was getting the materials stacked right to produce a topological state of matter. Instead of silicon, Microsoft’s topoconductor is made of indium arsenide, a material currently used in infrared detectors that possess special properties. Thanks to extreme cold, the semiconductor is combined with superconductivity to create a hybrid.

With a scaled quantum computer, Microsoft hopes to predict materials with even better properties for building the next generation of quantum computers beyond scale.

Microsoft has announced the development of Majorana 1, a quantum processor that utilizes topological qubits and promises a more straightforward approach to scaling quantum computing. The chip, which can be held in one’s hand, is designed with aluminum nanowires and fits neatly into a quantum computer deployable within Azure data centers.

One key advantage of Microsoft’s topological qubit architecture is its size. It operates within a “Goldilocks” zone, where it is neither too small nor too large for practical purposes. This simplifies building a scalable quantum machine by eliminating the need for intricate individual control lines.

Majorana 1 chip. Built-In error correction

The quantum chip (Majorana 1) is part of an ecosystem with control logic. It includes a dilution refrigerator for maintaining extremely low temperatures. There is also a software stack compatible with AI and classical computers. While further engineering work is required to refine these processes and achieve accelerated scale, many challenging scientific and engineering hurdles have already been overcome.

“From the start we wanted to make a quantum computer for commercial impact, not just thought leadership,”

Matthias Troyer, Microsoft technical fellow. Photo by John Brecher for Microsoft.

“We knew we needed a new qubit. We knew we had to scale.”

Producing the topological state of matter was one of the most difficult aspects. Microsoft’s top conductor, made of indium arsenide, requires precise alignment of atoms. This alignment is crucial to avoid defects that could destroy the qubit. Understanding these materials is complex. However, with a scaled quantum computer, researchers hope to predict materials with even better properties. These materials could be used for building future generations of quantum computers.

For those of a technological bent, the details of the chip are published in ArXiv: Roadmap to fault tolerant quantum computation using topological qubit arrays and you can learn more about the quantum ready program from Microsoft.

External Link: Click Here For More