As quantum computers become increasingly available through various platforms, researchers and end-users face difficulty selecting the best architecture and qubit technology for their specific needs. To address this challenge, scientists have developed methods to predict the expected performance of a target algorithm on a particular platform of hardware, allowing informed decisions about which device or subsystem to use.

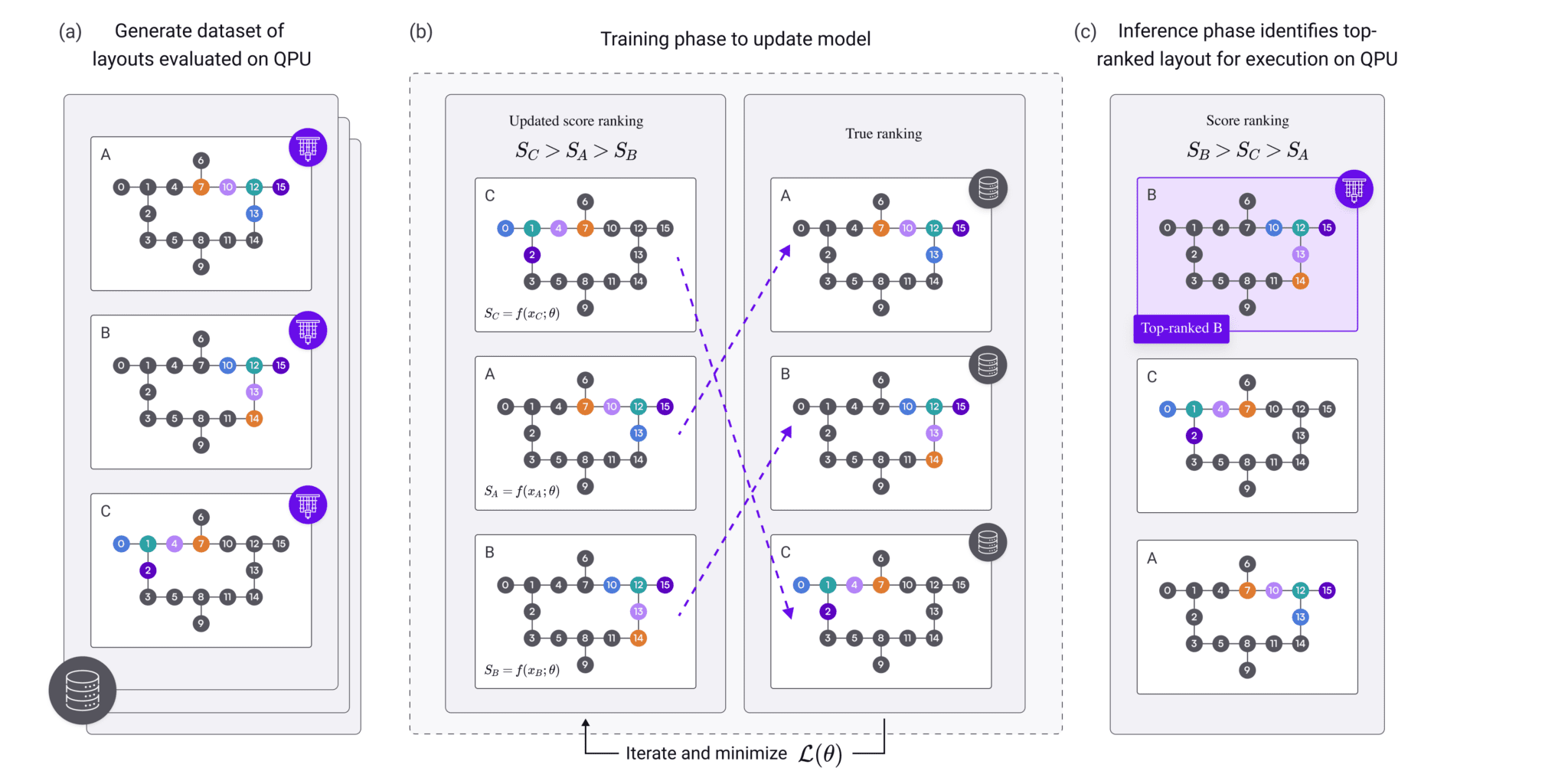

Recent research has demonstrated that machine learning can be used to rank quantum circuits for hardware-optimized performance enhancement. A team of researchers from QCTRL developed a machine learning-based method for ranking logically equivalent quantum circuits based on expected performance estimates derived from a training procedure conducted on real hardware.

The researchers’ approach consistently outperformed traditional methods, predicting layouts that exhibited lower noise and higher performance. Their results showed an 18% reduction in selection error compared to the baseline approach and a 32% reduction when compared to random selection. This breakthrough has significant implications for ensuring that researchers and end-users have access to the most accurate and reliable methods for selecting the best device or subsystem for their specific needs.

As the number and size of available quantum devices grow, this research will become increasingly important for unlocking the full potential of quantum computing. Further research directions include exploring the scalability of machine learning-based approaches to larger and more complex quantum systems, as well as developing more sophisticated models that take into account additional factors such as qubit noise and error correction mechanisms.

Quantum computers have become increasingly available through various platforms, including commercial, academic, and public sector initiatives. However, researchers and end-users face a daunting task in selecting the best architecture and qubit technology for their specific needs. This process involves assessing the relative performance advantages and disadvantages of each platform, synthesizing this information to choose a target hardware system for algorithmic execution.

As the number and size of available quantum devices grow, the question of how to select the best device or subsystem for executing a given quantum circuit becomes increasingly important. Ultimately, this process is an ideal target for automation and abstraction if suitable tools can be developed to predict the expected performance of a target algorithm on a hardware backend.

The topic of quantum computer benchmarking, also known as Quantum Characterization Validation and Verification (QCVV), aims to address this challenge by providing a framework for evaluating the performance of quantum computers. This involves developing methods to predict the expected performance of a target algorithm on a specific hardware platform, allowing researchers and end-users to make informed decisions about which device or subsystem to use.

Quantum circuit optimization refers to the process of selecting the most efficient layout for executing a quantum algorithm on a given hardware platform. This involves assigning abstracted qubits to physical qubits on a specific device, taking into account the characteristics of the device and the algorithm being executed.

The goal of quantum circuit optimization is to minimize errors and maximize performance by selecting the optimal layout for the algorithm. This process can be challenging due to the complex nature of quantum computers and the many variables that affect their performance.

Researchers have developed various methods for optimizing quantum circuits, including machine learning-based approaches that use real-world data to predict the expected performance of different layouts. These methods aim to identify the most efficient layout for executing a given algorithm on a specific hardware platform, taking into account factors such as device noise and errors.

Machine learning has emerged as a powerful tool for optimizing quantum circuits by providing a data-driven approach to predicting the expected performance of different layouts. Researchers have developed machine learning models that can be trained on real-world data to predict the fidelity of different layouts, taking into account factors such as device noise and errors.

One such model is the “circuit score” used in the study mentioned earlier, which is parameterized in terms of a physics-based phenomenological error model. This model is trained on a dataset of quantum circuits exhibiting a diversity of structures and executed on IBM hardware, allowing it to incorporate the contextual nature of real device noise and errors without the need for an exponentially costly tomographic protocol.

The machine learning model is then used to predict the fidelity of different layouts, taking into account factors such as device noise and errors. This approach has been shown to be highly effective in optimizing quantum circuits, with one study finding that it leads to a 18% reduction in selection error compared to a baseline approach and a 32% reduction when compared to random selection.

Quantum circuit optimization is a complex task that involves selecting the most efficient layout for executing a quantum algorithm on a given hardware platform. This process is challenging due to the many variables that affect the performance of quantum computers, including device noise and errors.

One key challenge in quantum circuit optimization is accounting for context-dependent and coherent gate errors, which can significantly impact the fidelity of different layouts. These errors are difficult to predict using simple proxy measures, making it challenging to develop effective methods for optimizing quantum circuits.

Another challenge is the need to balance the trade-off between minimizing errors and maximizing performance. This requires developing methods that can accurately predict the expected performance of different layouts, taking into account factors such as device noise and errors.

Quantum circuit optimization has significant implications for the development and deployment of quantum computers. By providing a framework for evaluating the performance of quantum computers, this approach can help researchers and end-users make informed decisions about which device or subsystem to use for executing specific algorithms.

This, in turn, can lead to improved performance and reduced errors in quantum computing applications, such as simulation and optimization problems. Additionally, quantum circuit optimization can help accelerate the development of new quantum algorithms and applications, by providing a more efficient and effective way to execute them on existing hardware platforms.

Quantum circuit optimization is an active area of research, with many potential future directions for improving this approach. One key direction is the development of more accurate machine learning models that can predict the expected performance of different layouts, taking into account factors such as device noise and errors.

Another direction is the exploration of new methods for optimizing quantum circuits, such as using reinforcement learning or other machine learning techniques to identify the most efficient layout for executing a given algorithm. Additionally, researchers are working on developing more effective ways to balance the trade-off between minimizing errors and maximizing performance in quantum circuit optimization.

Overall, quantum circuit optimization has significant implications for the development and deployment of quantum computers, and continued research in this area is likely to improve performance and reduce errors in quantum computing applications.

Publication details: “Learning to rank quantum circuits for hardware-optimized performance enhancement”

Publication Date: 2024-11-27

Authors: Gavin S. Hartnett, Aaron Barbosa, Pranav Mundada, Michael Hush, et al.

Source: Quantum

DOI: https://doi.org/10.22331/q-2024-11-27-1542