The increasing demands of artificial intelligence place significant strain on conventional computer designs, prompting a search for more efficient hardware solutions. Shahid Amin and Syed Pervez Hussnain Shah, both from Lahore Leads University, investigate this critical relationship between AI and computer architecture in a comprehensive survey of current and emerging technologies. Their work examines how specialised hardware, including graphics processing units, application-specific integrated circuits, and field-programmable gate arrays, accelerate complex AI tasks, while also analysing the core design principles that maximise performance and energy efficiency. By synthesising architectural approaches with benchmark data, the researchers present a clear picture of the evolving AI accelerator landscape and demonstrate that close collaboration between hardware and software development is now essential for continued progress in the field.

AI Hardware Accelerators And Emerging Trends

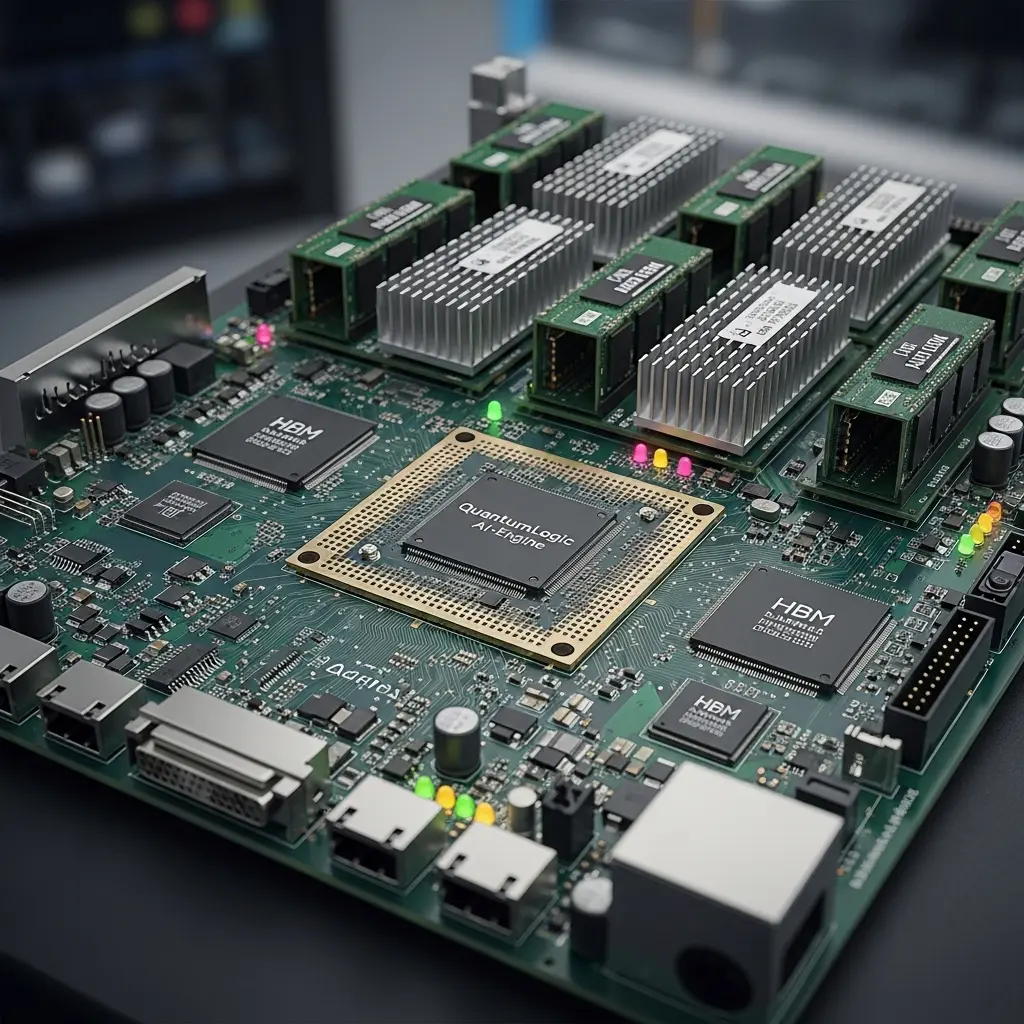

This extensive paper provides a comprehensive overview of the evolving landscape of AI hardware, detailing the architectures, trends, and challenges in accelerating artificial intelligence workloads. The research demonstrates a growing need for specialized hardware as traditional computing architectures struggle to meet the demands of modern AI, particularly deep learning. AI workloads require massive parallelism, high memory bandwidth, and energy efficiency, driving the development of dedicated accelerators. Key architectures explored include Graphics Processing Units, Application-Specific Integrated Circuits, and Field-Programmable Gate Arrays.

Near-Memory Computing and In-Memory Computing are also investigated, aiming to reduce data movement and improve energy efficiency, while Analog Computing and Neuromorphic Computing offer potentially revolutionary approaches to low-power AI. The study highlights several key trends and innovations, including Model-Chip Co-Design, where AI models and hardware are designed together for optimal performance, Sparsity and Quantization, reducing computational complexity by simplifying AI models, and 3D Stacking and Chiplets, increasing density and performance by combining multiple chips. Advanced Interconnects are also crucial, enabling high-bandwidth, low-latency communication between accelerators and memory, and Phase Splitting optimizes large language model inference by distributing the workload across multiple devices. The research concludes that the future of AI hardware will likely involve a combination of specialized accelerators, advanced interconnects, and novel computing paradigms, all working together to deliver unprecedented performance and efficiency.

AI Acceleration via Specialized Computer Architectures

The accelerating demands of Artificial Intelligence have driven significant innovation in computer architecture, prompting researchers to explore specialized hardware beyond traditional designs. Recent work focuses intensely on Graphics Processing Units, Application-Specific Integrated Circuits, and Field-Programmable Gate Arrays, each offering distinct advantages in accelerating modern AI workloads. Scientists systematically analyze these architectures, dissecting their design philosophies and key features to understand how they address the computational challenges of AI. A pivotal area of research centers on optimizing dataflow, advanced memory hierarchies, sparsity, and quantization, core principles for maximizing performance and energy efficiency.

For example, the Eyeriss architecture employs a novel Row-Stationary dataflow with a large number of processing elements and a global buffer, minimizing data movement and achieving a ten-fold improvement in energy efficiency compared to mobile GPUs when processing complex image data. Researchers also investigate extreme quantization techniques, like the FINN framework, which achieves ultra-low latency and high throughput by exploiting simplified data representation, enabling fast inference with low power consumption. Beyond individual architectural improvements, scientists increasingly emphasize hardware-software co-design, as demonstrated by new precision formats explicitly designed to work with software frameworks, doubling performance and memory efficiency for large language models. This work signals a mature industry trend where AI models and hardware are developed in tandem.

AI Hardware Accelerators And Dataflow Optimisation

The remarkable co-evolution of Artificial Intelligence and computer architecture has driven significant breakthroughs in hardware design, directly addressing the demands of increasingly complex AI models. This work details how specialized architectures are essential for maximizing performance and efficiency in modern AI workloads, moving beyond the limitations of traditional computing systems. Researchers have focused on three dominant paradigms, Graphics Processing Units, Application-Specific Integrated Circuits, and Field-Programmable Gate Arrays, analyzing their design philosophies and performance trade-offs to unlock new levels of computational power. Central to achieving efficiency is optimizing dataflow, carefully scheduling calculations and data movement to minimize data reuse and maximize processing speed.

Smart memory hierarchies, incorporating high-capacity High-Bandwidth Memory, large on-chip buffers, and fast local memory, are crucial for supporting these dataflows. Advanced interconnects further enhance performance by providing low-latency communication paths between multiple accelerator chips. Furthermore, techniques like sparsity exploitation and quantization significantly reduce computational load and memory bandwidth requirements. Rigorous testing and validation are achieved through industry-standard benchmarks, notably MLPerf, which provides a fair and objective assessment of AI system performance.

Comparative analysis reveals that the NVIDIA GB300 Blackwell achieves high throughput with low latency and excellent energy efficiency. The AMD MI355X and Intel Arc Pro B60 + Xeon 6 also demonstrate significant performance gains, while Google’s TPU v4 delivers a strong balance between throughput, latency, and energy efficiency. FPGAs like the Xilinx Alveo U50 offer flexibility but currently lag behind in throughput and energy efficiency. These results provide concrete evidence that specialized hardware is critical for achieving top-tier AI performance, with domain-specific designs consistently outperforming general-purpose CPUs.

AI Drives Collaborative Hardware-Software Codesign

The accelerating demands of artificial intelligence have instigated a fundamental shift in computer architecture, moving beyond traditional designs to specialized AI accelerators. This work surveys this evolution, charting the progression from straining the limitations of conventional systems to the development of Graphics Processing Units, Application-Specific Integrated Circuits, and Field-Programmable Gate Arrays. Analysis reveals that optimized dataflow, advanced memory hierarchies, and model optimization techniques are central to the efficiency of these architectures. A key finding is that artificial intelligence is now an integral partner in the design of computer hardware, necessitating a collaborative hardware-software co-design approach.

This means algorithms are developed considering hardware constraints, and hardware is architected to leverage algorithmic structures, a method that is no longer simply an optimization but a core requirement for future AI systems. The authors acknowledge that current accelerators, while powerful, are facing challenges from the continued growth in the complexity of AI models. Future research directions include Processing-in-Memory, which aims to eliminate data movement bottlenecks by performing computations directly within or near memory, and neuromorphic computing, inspired by the human brain. Neuromorphic systems utilize asynchronous, event-driven circuits and Spiking Neural Networks, potentially offering ultra-low-power computation for applications like always-on sensory processing.

🗞 The Role of Advanced Computer Architectures in Accelerating Artificial Intelligence Workloads

🧠 ArXiv: https://arxiv.org/abs/2511.10010