The pursuit of large-scale, fault-tolerant quantum computing relies heavily on efficient quantum error correction, and the surface code currently stands as a leading approach. Kohei Fujiu, Shota Nagayama, and Shin Nishio, alongside colleagues from Keio University and University College London, address a critical challenge in this field: the immense number of qubits required for practical implementation. Their work introduces a detailed method for densely packing multiple surface code components, reducing the physical qubit count and potentially lowering the resources needed for complex calculations. The team not only develops a concrete procedure for deforming and connecting these code patches, but also proposes a novel gate scheduling technique that minimises errors within the densely packed configuration, demonstrating through simulation that this approach can outperform standard surface codes in terms of logical error rates when combined with optimised syndrome extraction.

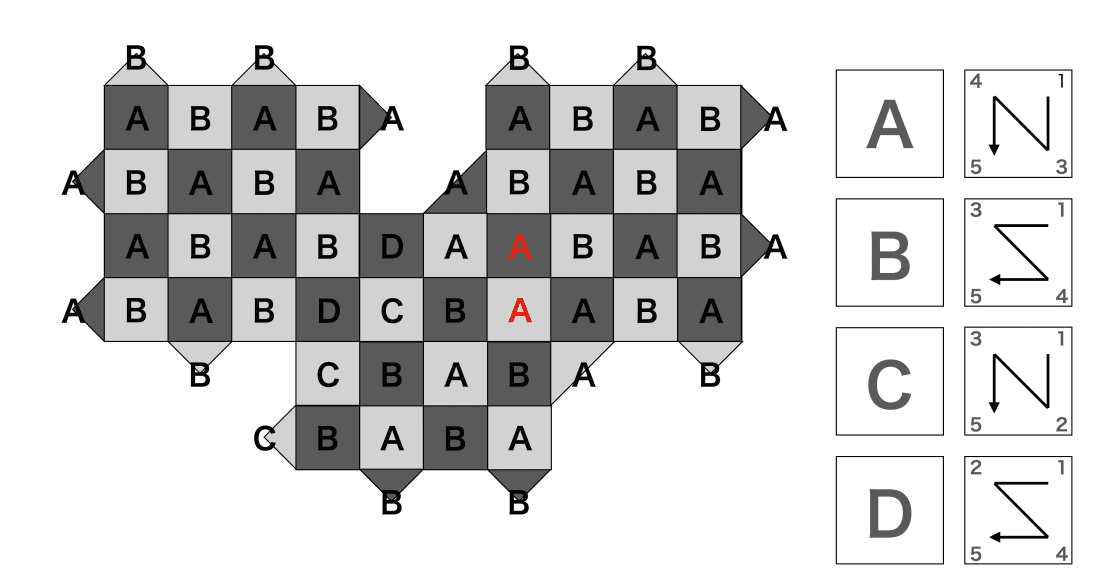

The research introduces methods for densely arranging the surface code on physical hardware, and scheduling quantum gates to minimise errors. This systematic approach allows the surface code to conform to arbitrary geometries and irregular qubit arrangements, improving qubit utilisation. The team developed code deformation procedures that optimise the physical layout while maintaining the logical structure, reducing the overall qubit count and simplifying wiring complexity.

Crucially, the method incorporates a novel gate scheduling algorithm that avoids “hook-errors”, which arise from improperly sequenced gates. The algorithm prioritises gate sequences that minimise the distance between interacting qubits, respecting the constraints of the deformed code layout. These techniques significantly reduce the overhead associated with implementing the surface code, achieving a substantial reduction in the number of physical qubits required to encode a logical qubit and improving the fidelity of quantum computations.

Densely Packed Surface Codes for Error Correction

The surface code is a leading quantum error correction code for realising large-scale fault-tolerant quantum computing. A major challenge is the extremely large number of qubits required, which this research addresses by investigating fusing multiple surface code patches into a densely packed configuration. This reduces the number of physical qubits needed per logical qubit to approximately three-fourths compared to standard arrangements. The researchers investigated the performance of deformed surface codes, focusing on the effects of deformation on the logical error rate. They employed numerical simulations to evaluate the code’s performance under realistic noise conditions, modelling both bit-flip and phase-flip errors and using the minimum-weight perfect matching algorithm for decoding. By systematically varying deformation parameters and noise levels, they mapped the code’s performance landscape and compared it to standard, non-deformed surface codes, incorporating realistic constraints on qubit connectivity. These simulations also assessed the scalability of the deformed codes, determining how performance changes as the code size increases, crucial for determining applicability to large-scale quantum computers.

Densely Packed Surface Codes Reduce Qubit Count

This research presents a detailed method for densely packing multiple surface code patches, a crucial step towards building practical, large-scale fault-tolerant quantum computers. The team successfully demonstrated a code deformation procedure that reduces the physical qubit count required for a given logical qubit, achieving an asymptotic reduction to three-fourths of that needed by standard, non-packed surface codes, addressing a significant challenge in quantum computing. The researchers also developed a novel gate scheduling technique specifically designed for these densely packed codes, mitigating the risk of error propagation caused by ‘hook’ errors. Through Monte Carlo simulations, the team confirmed that this hook-avoiding gate scheduling, combined with increasing code distance and reducing physical error rates, allows the densely packed surface code to achieve lower logical error rates than standard surface codes.

Sharing patch regions between logical qubits contributes to this improved performance by increasing the number of physical qubit errors required to induce a logical error. Future work will focus on evaluating a hierarchical memory microarchitecture that combines the space efficiency of dense packing for memory regions with the time efficiency of standalone surface codes for computation, and assessing compatibility with various surface code computing layouts. This research lays a strong foundation for developing more compact and efficient quantum computing architectures.

👉 More information

🗞 Dense packing of the surface code: code deformation procedures and hook-error-avoiding gate scheduling

🧠 ArXiv: https://arxiv.org/abs/2511.06758