The quest for faster clock frequencies has been a longstanding challenge in electronics. Researchers have made significant progress with superconducting circuits, pushing the boundaries of clock frequency. A recent study by Ikki Nagaoka and colleagues investigates the timing margin required to handle fluctuations and variations in superconductor single-flux-quantum (SFQ) gate-level-pipelined adders. The findings have significant implications for gate-level-pipelined circuits operating at lower clock frequencies, potentially enabling the development of faster, more powerful devices. This breakthrough has the potential to revolutionize the field of electronics and unlock new possibilities for future applications.

Can Superconducting Circuits Break the Clock Frequency Barrier?

The quest for faster clock frequencies has been a longstanding challenge in the field of electronics. With the advent of superconducting circuits, researchers have made significant progress in pushing the boundaries of clock frequency. In this study, Ikki Nagaoka and colleagues investigate the timing margin required to handle fluctuations and variations in superconductor single-flux-quantum (SFQ) gate-level-pipelined adders.

Timing Margin: The Key to Unlocking Higher Clock Frequencies

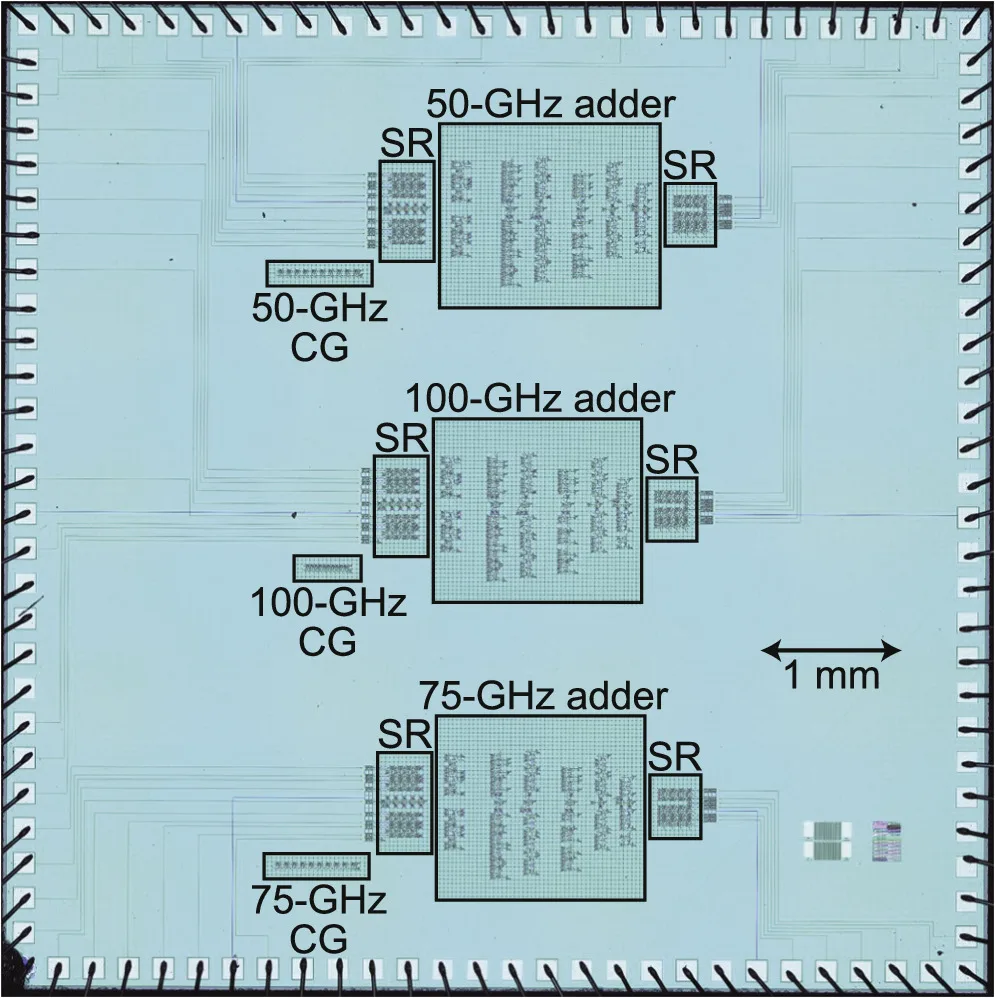

The timing margin refers to the amount of time required for a circuit to operate correctly despite fluctuations and variations. In this study, the researchers demonstrated three 4-bit adders with target clock frequencies of 50 GHz, 75 GHz, and 100 GHz using a 10 μm process. By estimating the required timing margin of these adders, they found that it was approximately 21 ps.

This finding has significant implications for gate-level-pipelined circuits operating at lower clock frequencies. Previously reported circuits operating at 30-60 GHz could potentially operate at higher clock frequencies by reducing their timing margins. This breakthrough has the potential to revolutionize the field of electronics and enable the development of faster, more powerful devices.

The Promise of Superconducting Circuits

Superconducting circuits have been gaining attention in recent years due to their potential to break the clock frequency barrier. SFQ logic is a type of superconducting circuit that uses voltage-pulse logic with fast switching times (10-12 s) and low energy consumption. This technology has shown great promise in enhancing clock frequency, making it an attractive solution for future electronics applications.

The Power-Wall Problem: A Major Obstacle to Overcoming

The power-wall problem is a major obstacle that has hindered the development of faster clock frequencies. As devices become smaller and more powerful, they require more energy to operate, leading to increased heat generation and reduced performance. Superconducting circuits offer a potential solution to this problem by reducing energy consumption and increasing efficiency.

Future Directions: Unlocking the Potential of Superconducting Circuits

While significant progress has been made in developing superconducting circuits, there are still many challenges to overcome before they can be widely adopted. Future research directions include improving the scalability and manufacturability of these circuits, as well as exploring new materials and technologies that can further enhance their performance.

Conclusion: The Future of Electronics is Bright

The study by Ikki Nagaoka and colleagues offers a glimpse into the exciting possibilities that superconducting circuits hold for the future of electronics. By pushing the boundaries of clock frequency and reducing energy consumption, these circuits have the potential to revolutionize the field and enable the development of faster, more powerful devices. As researchers continue to explore the potential of superconducting circuits, we can expect to see even more innovative applications in the years to come.

Publication details: “Investigation of timing margin in single-flux-quantum 4-bit adders for increasing clock frequency of gate-level-pipelined circuits”

Publication Date: 2024-05-02

Authors: Ikki Nagaoka, Tomoki Nakano, Ryota Kashima, Masamitsu Tanaka, et al.

Source: Applied physics express

DOI: https://doi.org/10.35848/1882-0786/ad46e5