The relentless growth of data transmission, fuelled by advances in artificial intelligence, demands increasingly sophisticated optical receivers and innovative integration technologies. Ye Gu, He Li, and Tinus Pannier, working at Ghent University and imec, alongside Shengpu Niu, Patrick Heise, and Christian Mai from IHP- Leibniz-Institut f ̈ur innovative Mikroelektronik, have achieved a breakthrough in this field by developing a 3D-integrated receiver that seamlessly combines electronic and photonic components. Their research pioneers the direct integration of a compact bipolar CMOS (BiCMOS) chip with a silicon photonics integrated circuit using micro-transfer printing, overcoming limitations inherent in traditional fabrication methods. The resulting receiver achieves a data rate of 224 Gb/s with exceptional sensitivity and power efficiency, representing a record-small footprint and a crucial advancement towards next-generation optical interconnects essential for the future of artificial intelligence.

Micro-Transfer Printed Optical Receiver for 224 Gbps

Scientists have developed a new optical receiver capable of transmitting data at 224 gigabits per second, a significant advancement for high-speed communication. The key innovation lies in a technique called micro-transfer printing, which allows for the stacking of tiny, specialized circuits, known as chiplets, to create a compact and efficient receiver. This receiver, built using a 130nm BiCMOS process, achieves exceptional performance through careful design and integration of these individual components. The receiver comprises multiple chiplets, each dedicated to a specific function, with a central focus on the transimpedance amplifier (TIA) chiplet.

The TIA converts the incoming optical signal into an electrical signal, a critical step for receiver sensitivity and bandwidth. This particular TIA design incorporates a shunt feedback structure for stability, an inductor to enhance performance, and a tunable resistor to compensate for manufacturing variations. This receiver achieves a data rate of 224 Gbps using a modulation technique called PAM-4, demonstrating a return loss of 53. 6 dBΩ, a responsivity of 0. 9A/W, and a sensitivity of -5.

2 dBm. Notably, the receiver consumes only 0. 51 pJ/bit, a remarkably low power consumption, and occupies an extremely small area of 0. 06 mm². These characteristics position it as a leading solution for high-speed data communication. Micro-transfer printing is central to this achievement, enabling the combination of different chiplets optimized for specific tasks. This 3D integration technique allows for high density, improved performance through shorter connections, and potentially lower costs compared to traditional methods.

Heterogeneous Integration via Micro-Transfer Printing

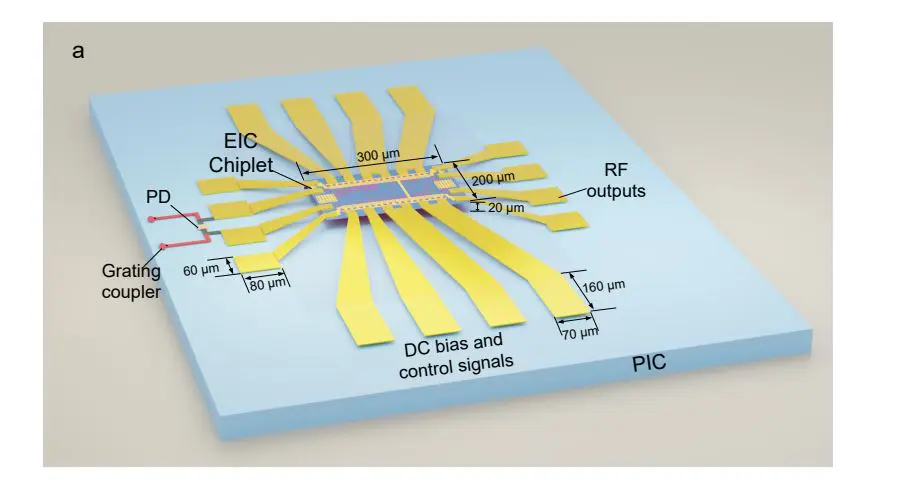

Researchers have demonstrated a groundbreaking 3D integration technique, successfully combining a compact electronic chiplet with a silicon integrated circuit using micro-transfer printing. This precise process overcomes limitations associated with fabricating components using different manufacturing processes, significantly enhancing performance and scalability. The fabrication process involves meticulous steps, including cleaning, applying a dielectric layer, precise chiplet placement, and curing. The resulting optical receiver incorporates a custom-designed electronic integrated circuit featuring a transimpedance amplifier, a variable gain amplifier, an output buffer, and circuitry for canceling unwanted signal bias.

Rather than a complex traveling wave circuit, the team employed a simpler, more power-efficient lumped-element circuit for the TIA. The variable gain amplifier amplifies the signal and converts it to a differential form, while the output buffer delivers the signal for measurement. A continuous-time linear equalizer compensates for signal loss at high frequencies. Measurements using a vector network analyzer revealed a 3-dB bandwidth of 51GHz and an output reflection coefficient below -8 dB up to 50GHz. Data transmission experiments demonstrated the receiver’s capabilities, achieving -11.

9 dBm and -9. 2 dBm optical modulation amplitude sensitivity at a bit-error rate of 2. 4×10−4 for 56 and 112 Gb/s modulations, respectively. Notably, the system achieved 224 Gb/s operation with a sensitivity of -5. 2 dBm and a power efficiency of 0. 51 pJ/b.

Gb/s Receiver via Heterogeneous Integration

Scientists have achieved a significant breakthrough in optical receiver technology, demonstrating a heterogeneously integrated system capable of 224 gigabits per second operation using four-level pulse amplitude modulation. This advancement addresses the increasing demands for data transmission driven by applications like artificial intelligence, offering a pathway to faster and more efficient optical transceivers. The research team successfully co-integrated a compact bipolar CMOS chiplet, measuring just 0. 06 square millimeters, directly onto a silicon integrated circuit using micro-transfer printing.

Measurements confirm the optical receiver achieves an outstanding -5. 2 dBm optical modulation amplitude sensitivity at a bit-error rate of 2. 4×10−4, establishing a record for footprint size and delivering excellent power efficiency of 0. 51 picojoules per bit. The resulting system exhibits a 51 gigahertz bandwidth, as confirmed by vector network analyzer measurements, and maintains an output reflection coefficient of less than -8 dB up to 50GHz.

Further data transmission experiments utilizing a pseudo-random bit sequence pattern demonstrate the system’s robust performance. The team achieved this high-speed operation with a compact chiplet footprint of 300 micrometers by 200 micrometers, enabled by small pads and the high alignment accuracy of the micro-transfer printing process. These results represent a critical step toward next-generation optical interconnects, offering a pathway to high-density, cost-efficient integration for the rapidly evolving field of artificial intelligence.

Compact 3D Receiver Achieves 224 Gigabits Per Second

This research demonstrates a novel approach to integrating electronic and photonic components, achieving a significant milestone in high-speed data transmission. By employing micro-transfer printing, the team successfully fabricated a 3D optical receiver capable of 224 gigabits per second operation using four-level pulse amplitude modulation. This receiver attains a record-low footprint and excellent power efficiency of 0. 51 picojoules per bit, representing a substantial improvement over existing integration methods. The achievement lies in the direct integration of a compact bipolar CMOS chiplet onto a silicon integrated circuit, overcoming limitations associated with traditional fabrication techniques.

This method not only enhances performance and scalability but also establishes a foundation for multi-terabit-per-second optical interconnects, crucial for next-generation computing and communication systems. The researchers acknowledge that while this work focuses on intensity-modulated direct-detection receivers, the integration technique holds promise for more complex receiver designs, including coherent systems capable of even higher data rates. Future work will likely explore the integration of multiple chiplets onto a single photonic integrated circuit to further increase total data throughput. The team highlights the potential for this technology to enable compact and energy-efficient designs, fostering innovation across a range of applications demanding high-performance data links.

🗞 A 3D-integrated BiCMOS-silicon photonics high-speed receiver realized using micro-transfer printing

🧠 ArXiv: https://arxiv.org/abs/2511.23196