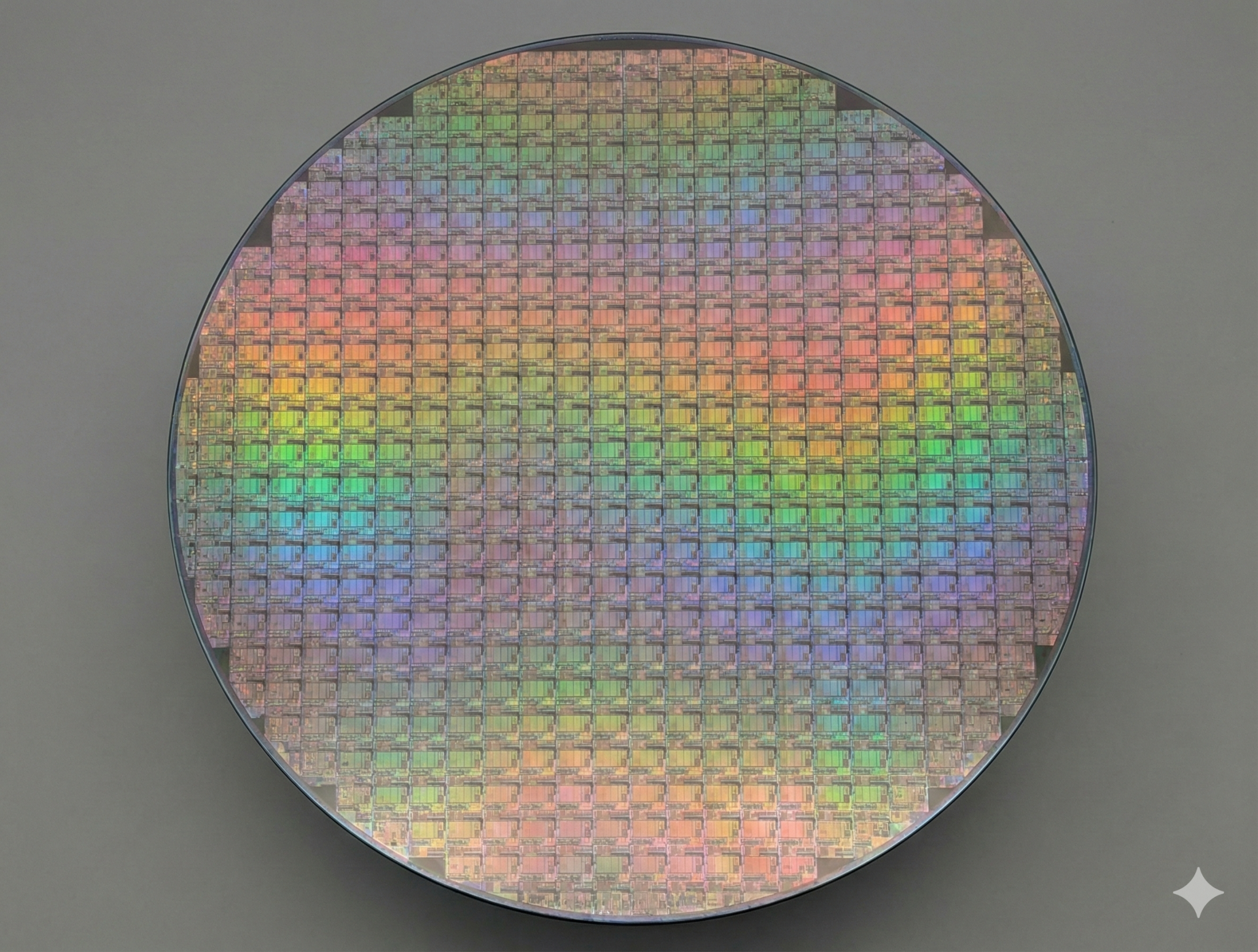

SEALSQCorp (NASDAQ: LAES) is strategically refocusing its quantum computing efforts on silicon-based architectures to leverage existing semiconductor technology, a move the company believes is crucial for long-term scalability. The Geneva-based developer of semiconductors, PKI, and post-quantum technology hardware and software is prioritizing silicon spin qubits and electrons-on-helium platforms, both of which can be fabricated and scaled using established CMOS processes. This emphasis on CMOS compatibility isn’t merely a manufacturing preference, but a system-level enabler for dense control arrays and high-speed signal routing necessary for quantum processors. “From our perspective, this technology alignment is a real advantage over other quantum approaches, such as superconducting or ion-trap systems,” said Carlos Moreira, Founder and CEO of SEALSQ, adding that silicon-based designs “are designed from the start to evolve within the semiconductor ecosystem.” Alongside hardware development, SEALSQ is also integrating post-quantum cryptography and hardware-based trust mechanisms to ensure secure quantum systems.

SEALSQ Focuses on CMOS-Compatible Quantum Architectures

SEALSQCorp is intensifying its focus on developing quantum computing architectures deeply compatible with complementary metal-oxide-semiconductor (CMOS) technology, a move signaling a commitment to long-term scalability within the rapidly evolving quantum landscape. The Geneva-based company, trading on NASDAQ as LAES, believes aligning quantum processors with established semiconductor manufacturing processes is crucial for practical advancement, specifically concentrating investments on silicon spin qubits and electrons-on-helium platforms. These approaches offer a pathway to fabrication, integration, and scaling using existing CMOS capabilities, a significant advantage over other quantum modalities. Both silicon spin qubits and electrons-on-helium architectures present promising avenues for CMOS compatibility; the former leverages electrons in silicon using chip-making methods akin to CMOS, while the latter employs electrons above superfluid helium on a silicon chip with CMOS-compatible controls.

According to SEALSQ, CMOS compatibility extends beyond mere manufacturing preference, functioning as a “system-level enabler” for the dense arrays of control electrodes, high-speed signal routing, and cryogenic-compatible electronics required by quantum processors. The company is also exploring Fully Depleted Silicon on Insulator (FDSOI) technology, believing it offers a strong compromise for acceptable noise and power consumption levels. Simultaneously, SEALSQ is integrating post-quantum cryptography (PQC) and hardware-based trust mechanisms into its system architecture, recognizing the critical need for robust security as quantum computers scale.

Silicon Spin Qubits & Electrons-on-Helium Platforms Compared

This commitment isn’t simply about manufacturing preference, but a fundamental architectural decision, recognizing that long-term scalability hinges on alignment with established semiconductor technology. This approach allows for the co-design and eventual co-integration of quantum devices with classical CMOS control circuitry, a significant step toward practical quantum computing.

FDSOI Technology Enables Low-Noise Quantum Control

Both technologies benefit from the potential for fabrication using established CMOS processes, a key factor in SEALSQ’s long-term strategy. FDSOI, a wafer-level semiconductor technique employing a thin silicon layer atop an insulating layer, is proving advantageous in reducing power consumption and minimizing noise—critical considerations for maintaining qubit coherence. This focus isn’t simply a manufacturing preference, but a systemic necessity, as quantum processors demand dense control electrode arrays, rapid signal routing, and cryogenic-compatible electronics. This holistic approach—combining scalable CMOS-based quantum architectures with embedded PQC—positions SEALSQ to deliver secure, trustworthy quantum solutions for critical infrastructure and beyond.

Post-Quantum Cryptography Integrated for System Security

SEALSQCorp is proactively embedding post-quantum cryptography (PQC) directly into the architecture of its developing quantum systems, recognizing that robust security must be foundational, not an afterthought, as these processors scale. This integration addresses the looming threat to current public-key cryptography posed by increasingly powerful quantum computers, ensuring resilience against both conventional and quantum-enabled attacks on sensitive data like firmware updates and calibration data. The company’s approach is particularly crucial for distributed quantum systems, where secure exchange of information between control electronics, cryogenic interfaces, and cloud orchestration layers is paramount. Beyond simply implementing PQC algorithms, SEALSQ is leveraging secure elements fabricated alongside quantum control circuitry to enable trusted boot, device attestation, and secure key storage. This ensures that only authorized software and operators can access or modify quantum systems, a capability vital as these computers transition from research labs to critical infrastructure.

Securing FPGA configurations used in qubit manipulation, such as error treatment algorithms, is also a key component of this holistic security strategy. This convergence aims to create quantum machines that are not only powerful but also inherently secure and trustworthy for deployment in sensitive sectors.

The intrinsic physical properties of silicon, particularly its well-understood band structure, minimize environmental coupling noise compared to some solid-state alternatives. When spin qubits are implemented using isotopically enriched silicon (e.g., Si-28), the natural abundance of nuclear spins—which typically contribute significant decoherence—can be suppressed. This isotopic purification is a key scientific requirement, as it dramatically extends the qubit coherence times ($T_2$), pushing the solid-state architecture closer to fault-tolerant operational regimes necessary for complex algorithms.

Furthermore, utilizing CMOS processes allows for the monolithic integration of classical control electronics and quantum components onto a single chip, a concept known as co-integration. This drastically reduces the latency associated with long-range wiring and intermediary interfaces, which is a significant bottleneck in scaling complex quantum circuits. Such integration enables a more efficient power budget and a more tightly controlled local operating environment critical for minimizing crosstalk and managing the signal integrity across dense arrays of quantum elements.

A major technical challenge remains the efficient manipulation and readout of individual qubits within a cryostatically cooled environment. The system requires highly precise microwave or voltage pulses, demanding sophisticated quantum control electronics operating at millikelvin temperatures. SEALSQ’s focus on established CMOS platforms is aimed at providing the necessary infrastructure to manage the complex interplay between high-frequency classical control lines and the ultra-sensitive quantum state measurements inherent to the underlying physics.

From a broader industry perspective, the emphasis on silicon represents a technological convergence: marrying the maturity of microelectronics manufacturing with cutting-edge quantum physics. This approach transforms quantum computing from a purely academic research pursuit into an industrial engineering problem, allowing for the predictable, wafer-scale production necessary to achieve quantum advantage and commercial viability beyond laboratory demonstrations.

From our perspective, this technology alignment is a real advantage over other quantum approaches, such as superconducting or ion-trap systems. While those platforms are scientifically impressive, they often depend on specialized materials, custom fabrication steps, or complex optical and vacuum setups that do not align as naturally with mainstream semiconductor manufacturing.

Carlos Moreira, Founder and CEO of SEALSQ