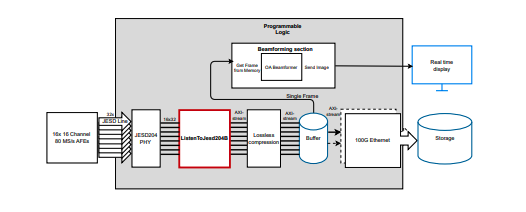

Ultrasound imaging increasingly demands systems capable of processing data from hundreds of synchronized channels at very high speeds, pushing the limits of traditional data transfer methods. Soumyo Bhattacharjee, Federico Villani, Christian Vogt, and colleagues at ETH Zurich address this challenge with the development of ListenToJESD204B, a new open-source IP core designed for use in FPGA-based ultrasound acquisition systems. This core implements the JESD204B serial interface, offering a significant advantage over proprietary commercial options which are often expensive and resource-intensive. ListenToJESD204B achieves comparable performance while dramatically reducing hardware requirements, occupying only a fraction of the configurable logic blocks needed by existing solutions, and its open-source nature promises to accelerate innovation in medical imaging technology. The team successfully demonstrates stable, error-free data streaming at high speeds, paving the way for more affordable and accessible ultrasound systems.

Analogue signal links present challenges related to bandwidth, pin count, and latency. While the JESD204B serial interface addresses these limitations, commercially available FPGA IP cores are often proprietary, costly, and resource-intensive. This work introduces ListenToJESD204B, an open-source receiver IP core released under a permissive Solderpad 0. 51 license, specifically designed for AMD Xilinx Zynq UltraScale+ devices. The core, written in synthesizable SystemVerilog, supports four GTH/GTY lanes operating at 12.8 Gb/s and delivers cycle-accurate AXI-Stream data alongside deterministic Sub-class 1 latency. Notably, it occupies only 107 configurable logic blocks, equivalent to approximately 437 LUTs, representing a 79% reduction in resource usage compared to similar commercially available IP. A modular data path further enhances its adaptability and efficiency.

Open-Source JESD204B Receiver Core Implementation

Researchers have developed a comprehensive JESD204B receiver IP core, addressing a critical need for accessible and efficient high-speed data transfer. The core provides an open-source solution to the challenges posed by expensive and inflexible commercial alternatives, particularly for applications like modern imaging systems. The focus on Subclass 1, which ensures deterministic latency, makes it well-suited for real-time applications requiring precise timing. Key benefits include its open-source nature, promoting collaboration and customization, its resource efficiency, allowing for more channels or processing on an FPGA, and its support for Subclass 1, critical for predictable latency.

The core is implemented in synthesizable SystemVerilog and targets Xilinx UltraScale+ ZU19EG FPGAs. It supports up to four lanes, operates at 12 Gbps, and features a modular design. Rigorous verification involved both simulation and hardware-in-the-loop testing. Performance testing demonstrates that the core meets timing requirements at 320 MHz, achieving significantly lower utilization of logic resources and registers compared to the Xilinx commercial IP core. It exhibits a startup latency of 13 clock cycles, with throughput matching the Xilinx IP core after startup.

The comprehensive documentation, strong motivation, detailed comparison, open-source availability, and hardware validation all contribute to the strength of this work. Potential areas for future development include exploring support for additional JESD204B subclasses, detailing error handling mechanisms, clarifying configuration options, assessing scalability to larger channel counts, and providing more information about the modular testbench framework. Investigating power consumption, integrating the receiver with an optical interface, and demonstrating the core in a real-world application would further enhance its impact. This research represents a valuable contribution to the field, offering a resource-efficient and accessible solution for high-speed data acquisition.

Low-Latency Receiver Core for High-Speed Data

Researchers have developed a new receiver core, ListenToJESD204B, designed to handle the demanding data rates of modern ultrasound systems and other high-speed data acquisition applications. Current data links struggle to keep pace with the increasing need for numerous synchronized channels operating at tens of millions of samples per second, and existing solutions often come with high costs and limited flexibility. This new core addresses these challenges by providing an open-source alternative that significantly reduces resource requirements. The core operates by receiving data through multiple high-speed lanes, processing it, and then delivering it in a standardized format for further analysis.

Crucially, it achieves deterministic, low-latency performance, essential for precise timing in applications like ultrasound imaging, and maintains synchronization between channels. Verification against industry-standard IP cores and hardware testing with analog-to-digital converters confirms its adherence to the JESD204B protocol. Long-term stability tests, running for half an hour, demonstrated error-free operation, validating its reliability in continuous acquisition scenarios. The core’s efficiency is particularly noteworthy; it requires substantially fewer logic resources, approximately 21% of the LUTs and registers, compared to commercially available alternatives.

This reduction in resource usage allows for a greater number of acquisition channels to be implemented on a single FPGA, or frees up valuable space for more complex signal processing algorithms. In practical tests, the core successfully processed data from a 32-channel ultrasound transducer, accurately reconstructing waveforms and even imaging internal structures within a tissue-mimicking phantom. The core’s performance meets the stringent timing requirements of the JESD204B standard, operating at a clock rate of 320 MHz with minimal delay. This combination of low resource usage, deterministic performance, and successful validation makes ListenToJESD204B a compelling solution for developers seeking a flexible and cost-effective data acquisition interface, particularly in the rapidly evolving field of medical imaging and beyond. The open-source nature of the core further encourages collaboration and innovation within the community.

Efficient JESD204B Receiver for Zynq FPGAs

The research team presents ListenToJESD204B, a new open-source receiver IP core designed for Xilinx Zynq UltraScale+ devices. This core implements the JESD204B protocol, enabling high-speed data transfer crucial for applications like ultrasound imaging, and supports up to four data lanes operating at 12. 8 Gb/s. Importantly, the design achieves a significant reduction in resource utilisation, requiring only a fraction of the logic blocks compared to commercially available alternatives, thereby allowing for more channels or increased processing capability within the same FPGA. The core’s modular architecture and efficient implementation facilitate stable, high-throughput data streaming, demonstrated by successful testing with analog-to-digital converters and sustained operation at 80 MSPS.

The authors acknowledge a fixed startup latency of 13 clock cycles before valid samples appear, but highlight that subsequent throughput matches established commercial IP cores. Future work could extend the core’s functionality to support additional JESD204 protocol modes and develop a complementary transmitter, alongside a reusable testbench framework to streamline verification of both current and future designs. The open-source nature of ListenToJESD204B, released under a permissive license, promotes accessibility and collaboration within the research community.

🗞 ListenToJESD204B: A Lightweight Open-Source JESD204B IP Core for FPGA-Based Ultrasound Acquisition systems

🧠 ArXiv: https://arxiv.org/abs/2508.14798