Quantum error correction remains vital for building practical quantum computers, and recent attention focuses on a promising approach using quantum low-density parity-check codes. Bane Vasic from the University of Arizona, Valentin Savin from Université Grenoble Alpes, and Michele Pacenti from the University of Arizona, alongside Shantom Borah and Nithin Raveendran, investigate these codes which offer the potential for significantly reduced overhead compared to traditional methods. Their work addresses a critical need for codes that not only correct errors effectively, but also align with the specific constraints of real-world quantum hardware, such as its connectivity and inherent noise. By exploring the theoretical foundations and practical construction of these codes, the team demonstrates a pathway towards fault-tolerant quantum computation with improved efficiency and scalability, representing a significant step forward in the field of quantum information science.

Correcting Errors in Noisy Memories

This study investigates the construction of stable memories capable of retaining information despite the inherent unreliability of physical components, and develops a framework for analyzing the performance of error-correcting codes within these memories. Researchers model a memory comprised of n bits, where each bit may flip with a certain probability over time. The accumulation of errors threatens to corrupt the stored information, and the team investigates applying error correction at regular intervals to maintain data integrity. Their approach involves a three-stage correction circuit: syndrome computation, iterative decoding, and recovery.

The syndrome identifies potential errors, while the decoder estimates the error vector, and the recovery operation applies the estimated correction. The effectiveness of this circuit depends on the decoder’s ability to accurately identify and correct errors, minimizing residual errors after each correction round. Researchers consider the speed of the correction circuit relative to the memory, emphasizing that the correction process must be completed within each memory cycle to ensure stability. The ability to perform multiple correction rounds within a given timeframe is crucial for preserving information over extended periods, and the team’s framework provides a means to evaluate the trade-offs between correction speed, circuit complexity, and memory stability. This analysis allows for a comprehensive understanding of the factors influencing the performance of error-correcting codes in noisy memory systems.

Fault-Tolerant Memory With Unreliable Components

Scientists have achieved a breakthrough in coded memory design, demonstrating stable information storage even when all components of the correction circuitry are unreliable. This work establishes that memories can maintain data integrity through specifically designed error-correcting codes, despite the presence of faults. The research centers on low-density parity-check (LDPC) codes, which enable remarkably shallow computational depth in correction circuits. Experiments reveal that the structure of LDPC codes allows syndrome computation and decoding to be performed using constant-depth Boolean circuits, meaning the number of computational steps remains bounded regardless of the code’s size.

This ensures the correction process can keep pace with the memory’s clock speed. Measurements confirm that the performance of these coded memories is not limited by the reliability of individual components, but by the overall structure of the code and the efficiency of the correction circuitry. Researchers demonstrated that by carefully selecting codes with constant row-weight and column-weight, the depth of the correction circuits can be kept bounded, minimizing the probability of errors during correction. This breakthrough delivers a pathway to fault-tolerant memories where the coding rate can be adjusted to balance computation and memory errors, ensuring stable data storage. The results demonstrate that the fundamental properties of LDPC codes, particularly their low-density structure, are conducive to building resilient and fault-tolerant memories.

QLDPC Codes Enable Constant Overhead Tolerance

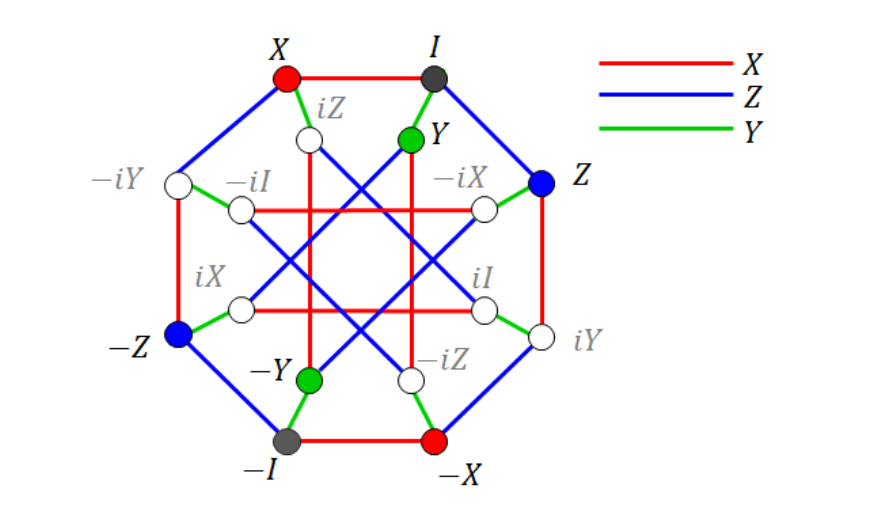

This work details significant advances in quantum error correction through the exploration of low-density parity-check (QLDPC) codes. Researchers have demonstrated the potential of these codes to overcome limitations previously encountered in achieving scalable and efficient quantum computation. By drawing parallels with classical LDPC codes, the team has leveraged established decoding techniques and performance benchmarks to inform the development of quantum counterparts, paving the way for more robust quantum information processing. The investigation highlights the promise of constant overhead fault tolerance, a crucial step towards building practical quantum computers capable of handling complex calculations.

The study establishes a strong connection between classical and quantum fault-tolerance, revealing underlying principles common to both fields. This approach allows for the application of classical insights to address challenges in quantum error correction, streamlining the development process and fostering a deeper understanding of error mitigation strategies. While acknowledging the complexities of finite-length code construction and the need to account for specific hardware characteristics, the research provides a comprehensive overview of QLDPC codes and their iterative decoders, offering a valuable resource for the information theory community. Future progress will depend on addressing the challenges of tailoring these codes to the nuances of real-world quantum hardware, and optimizing code performance in realistic environments. Despite these challenges, this work represents a substantial step forward in the pursuit of reliable and scalable quantum computation.

🗞 Quantum Low-Density Parity-Check Codes

🧠 ArXiv: https://arxiv.org/abs/2510.14090