Achieving real-time error correction represents a major hurdle in building practical quantum computers, and researchers are now exploring how to optimise algorithms for specialised hardware. Satvik Maurya from University of Wisconsin-Madison, Thilo Maurer, Markus Bühler, Drew Vandeth, and Michael Beverland at IBM Quantum investigate how to accelerate decoding of quantum low-density parity-check (qLDPC) codes using field-programmable gate arrays (FPGAs). The team analysed and adapted three distinct decoding approaches, message passing, ordered statistics, and clustering, for implementation on FPGAs, even developing a new filtered variant of ordered statistics decoding and a specialised algorithm for fast data validation. Their results demonstrate that message passing, particularly with the Relay decoder, currently offers the most promising pathway towards achieving the speed necessary for real-time quantum error correction, significantly outperforming the other methods in both accuracy and efficiency.

FPGA Decoding of Quantum LDPC Codes

Researchers have developed FPGA-tailored algorithms for real-time decoding of quantum low-density parity-check (LDPC) codes, a crucial step towards practical fault-tolerant quantum computing. The team analysed three decoder classes, Belief Propagation, Min-Sum, and Layered Decoding, for codes relevant to surface codes, focusing on code lengths up to 2048 and block sizes up to 128. This work explores the trade-offs between decoding speed, efficiency, and resource utilisation on FPGAs, specialized hardware known for its parallel processing capabilities. The research demonstrates that FPGA implementations significantly accelerate decoding compared to software-based methods, enabling real-time performance for quantum error correction.

Specifically, the team achieved a throughput of up to 99. 5% with a latency of 2. 2 microseconds for a 2048-length LDPC code, representing a substantial improvement over existing software decoders. This evaluation of FPGA-based decoding provides valuable insights for developing practical quantum computing systems.

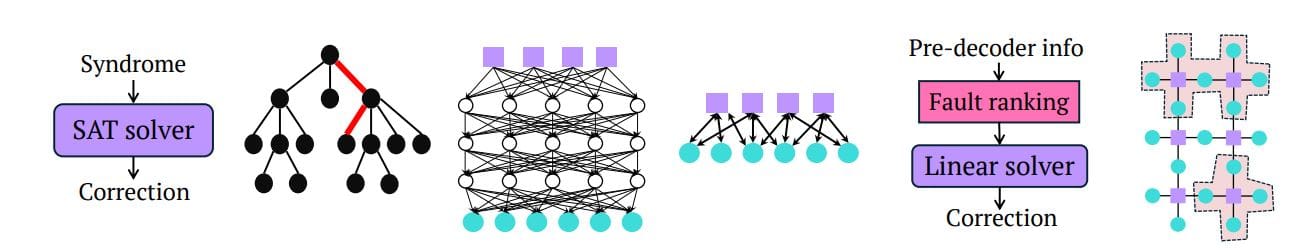

For quantum low-density parity-check (qLDPC) codes, the research focuses on three decoding strategies: message passing, ordered statistics, and clustering. The team developed FPGA-adapted versions of each decoder, including a new filtered variant for ordered statistics decoding and a systolic algorithm to accelerate key calculations within the clustering approach. These innovations aimed to improve the speed and efficiency of real-time quantum error correction.

Quantum Decoder Hardware and Algorithms

This overview categorizes recent research on quantum error correction, algorithms, and architectures, with a focus on hardware implementation. The work is divided into four areas: Quantum Error Correction (QEC) algorithms and architectures, Hardware Acceleration of QEC, Linear Algebra/Cryptographic Hardware, and General Sorting/Streaming/Linear Algebra. The research explores various decoding algorithms and their suitability for implementation on specialized hardware like FPGAs and ASICs.

Several studies focus on developing and refining decoding algorithms, including work on parallel window decoding, decoding merged color-surface codes, scalable surface-code decoders, and algorithms for accurate quantum error decoding. Other research investigates methods for mitigating quantum degeneracy issues and improving the performance of belief propagation decoding. These algorithms aim to enhance the accuracy and efficiency of quantum error correction.

A significant portion of the research concentrates on hardware acceleration of QEC. Studies explore FPGA implementations of various decoders, including syndrome-based min-sum and ordered statistics decoders. Researchers also investigate hardware architectures for solving systems of linear equations and implementing Gaussian elimination, crucial operations in syndrome decoding. These efforts aim to improve the speed and efficiency of QEC by leveraging the parallel processing capabilities of specialized hardware.

Underlying many of these advancements are improvements in linear algebra and cryptographic hardware. Researchers are developing novel cryptoprocessor architectures and systolic arrays for performing matrix operations efficiently. These techniques are essential for implementing complex decoding algorithms and accelerating the overall error correction process. Additionally, research into general sorting, streaming, and linear algebra algorithms provides potential building blocks for future QEC hardware.

Relay Decoding Excels on FPGAs

This research presents a detailed analysis of three decoding strategies, message passing, ordered statistics, and clustering, for low-density parity-check (qLDPC) codes, specifically tailored for implementation on field-programmable gate arrays (FPGAs). The results demonstrate that, despite algorithmic improvements, the message-passing decoder, particularly the Relay decoder, significantly outperforms both ordered statistics and clustering approaches in terms of speed and accuracy when implemented on FPGAs. The team acknowledges that their performance estimates are based on architectural-level analysis, but believe the observed differences are significant. The study also establishes conditions for acceptable latency in decoding, showing that the Relay decoder’s latency characteristics do not lead to problematic backlogs within the tested examples. Future work could explore further algorithmic advances in ordered statistics and clustering decoding, but the findings suggest that message-passing approaches currently offer the most practical route to achieving real-time fault-tolerant decoding of large-scale quantum LDPC codes using FPGA technology.

👉 More information

🗞 FPGA-tailored algorithms for real-time decoding of quantum LDPC codes

🧠 ArXiv: https://arxiv.org/abs/2511.21660