Researchers from NTT Corporation, the University of Tokyo, Kyushu University, and RIKEN have developed a new quantum computing architecture. It separates memory and processor using a load-store design, replacing conventional circuit-based methods.

This innovation addresses scaling, memory utilization, and portability challenges. It reduces resource requirements by approximately 40%, achieves a practical memory efficiency of around 90%, and increases computation time minimally by about 5%. The findings were presented at the 31st IEEE International Symposium on High-Performance Computer Architecture in March 2025.

NTT Introduces New Quantum Computing Architecture Separating Memory and Processor

NTT has introduced a novel quantum computing architecture that separates memory and processor, significantly departing from traditional designs. This innovation aims to enhance efficiency and scalability in quantum computing systems.

Conventional quantum computer designs rely on quantum circuits, which present challenges in scaling due to the need for continuous operation across expanding systems. Additionally, these systems are optimized for specific device sizes and error correction methods, limiting their portability between different architectures.

The new architecture employs a load-store approach, akin to classical computers, where memory and the processor operate independently. This method facilitates efficient data exchange. It achieves this through load and store instructions. Memory utilization is improved by dedicating memory solely to data storage rather than operations.

To further optimize performance, the researchers introduced novel quantum memory techniques, including row access and point access types. These methods achieve asymptotic memory efficiency of 100% and practical efficiency of around 90%, significantly enhancing resource management.

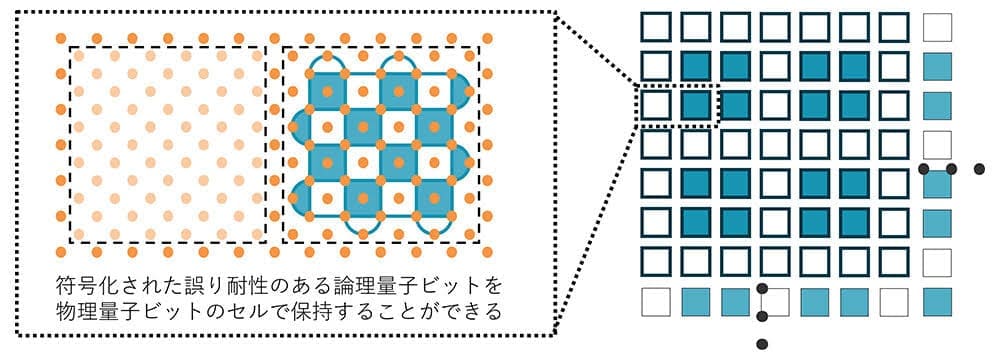

Surface codes are the error correction method currently undergoing the most research and development in terms of how to realize fault-tolerant quantum computers. However, this method requires a very large number of physical quantum bits, which has been a major challenge in terms of the feasibility of implementing it on a computer large enough to achieve quantum acceleration. This research proposes a quantum computer version of a load-store architecture that utilizes the theoretical properties of surface codes and knowledge of computer design, thereby solving this problem by halving the number of physical quantum bits required without compromising the performance of quantum computing. This is the result of interdisciplinary collaboration through collaboration between projects within Moonshot Research, and can be said to be a major step forward toward the realization of large-scale fault-tolerant quantum computing.

Comment from PM Tsuyoshi Yamamoto

Despite these advancements, the impact on computation time remains minimal, with an increase of approximately 5%. This balance between efficiency and performance underscores the practicality of the new architecture.

The broader significance of this work lies in demonstrating that fundamental computer architecture principles can be effectively applied to quantum computing. This breakthrough will catalyze further research and development, potentially establishing a foundational design for future quantum systems.

The Problems with Conventional Quantum Computer Design

Conventional quantum computer designs face significant scalability and resource management challenges due to their reliance on quantum circuits. These systems require continuous operation across expanding networks of qubits, making it difficult to maintain coherence and control as the system grows. Additionally, traditional architectures are often optimized for specific device sizes and error correction methods, limiting their adaptability and portability between different hardware implementations.

Memory utilization in conventional designs is inefficient, further exacerbates these issues. In quantum circuits, memory is frequently entangled with computational operations, reducing its ability to function as a dedicated storage resource. This entanglement complicates data management and limits the system’s capacity for efficient information processing.

These limitations highlight the need for alternative approaches that can address scalability, portability, and resource efficiency in quantum computing architecture. The transition to architectures that separate memory and processor operations represents a potential solution to these persistent challenges.

NTTs Load-Store Approach for Efficient Quantum Computing

To optimize performance, the researchers implemented novel quantum memory techniques, including row access and point access methods. These innovations achieve asymptotic memory efficiency of 100% and practical efficiency around 90%, significantly enhancing resource utilization compared to conventional designs.

One of the contributions of theoretical research towards the realization of large-scale fault-tolerant quantum computers is the presentation of a quantum computer architecture that is both versatile and scalable, built on fundamental research. This research proposes such an architecture by reconsidering the configuration of quantum computers based on the mechanisms of modern conventional computers and the characteristics and properties of quantum mechanics, and by redefining the functions of quantum computer memory and processors. This result is a key to bridging the gap between theory and implementation in the field of quantum computing, which continues to develop remarkably, and is a unique gift of this project, which was made possible by the work of a team of researchers with diverse backgrounds.

Comment from Masato Oashi

The impact on computation time remains minimal, with an increase of approximately 5%. This balance between efficiency and performance demonstrates the practicality of the new architecture for real-world applications. The approach also addresses scalability challenges inherent in traditional quantum computing systems by simplifying data management and reducing operational complexity.

By applying fundamental principles of computer architecture to quantum systems, NTT’s innovation opens new avenues for research and development in quantum computing. This work highlights the potential for established architectural concepts to enhance quantum technologies, potentially establishing a foundational design for future quantum systems.

Right: The blue cells represent logical quantum bits, and the white cells represent auxiliary cells assigned to the calculations. Here, memory efficiency is measured as the ratio of the number of blue cells to the total number of cells. The memory efficiency of the design guideline shown in the figure is 44%.

Reducing the amount of hardware resources required is extremely important in quickly realizing fault-tolerant quantum computers. This research proposes a quantum computer architecture that utilizes the properties of surface codes from the perspective of computer design, without changing the surface codes themselves or the required specifications for the hardware, to reduce the number of qubits by up to half without significantly increasing execution time. This result will have a major impact, as it updates the assumptions made in estimating quantum computing resources based on implementation. This is an initiative unique to moonshot research, which brings together researchers with diverse backgrounds, and further developmental discussions are expected.

PM Comment from Shota Nagayama

Key Points of the Announcement

- Introduces a new quantum computer architecture that separates memory and processors while adhering to the quantum mechanical constraint that “copying is not possible.”

- Proposes a versatile, portable, load-store, fault-tolerant quantum computer design.

- Demonstrates that computing time increases by only ~3% while reducing hardware scale by ~40% compared to conventional quantum computers.

- Expected to contribute to quantum computer architecture research and accelerate the development of fault-tolerant quantum computing.

- The study introduces a load-store quantum computing architecture, inspired by conventional computing principles.

Research Overview

- Conducted by a collaborative team from the University of Tokyo, Nippon Telegraph and Telephone Corporation, RIKEN Quantum Computing Research Center, and Kyushu University.

- Applies the load-store concept from classical computing to quantum computing.

- Enhances program portability and enables efficient quantum hardware use.

- Expected to facilitate early realization of practical quantum computing.

- Research findings to be presented at HPCA2025 (IEEE International Symposium on High-Performance Computer Architecture).

Conference Presentation & Publication

- Research to be presented at HPCA2025 under the title:

“LSQCA: Resource-Efficient Load/Store Architecture for Limited-Scale Fault-Tolerant Quantum Computing.” - Authors: Takumi Kobori, Yasunari Suzuki, Yosuke Ueno, Teruo Tanimoto, Synge Todo, Yuuki Tokunaga.

This research bridges the gap between theoretical quantum computing and practical implementation by redefining the roles of memory and processors in quantum systems.

More information

External Link: Click Here For More