MicroCloud Hologram Inc. achieved efficient quantum spin model simulation on classical hardware by utilizing field programmable gate arrays (FPGA). The company converted quantum tensor network algorithms into parallel computing circuits on FPGA, accelerating tensor network computing. This innovation offers a new approach for quantum physics research and quantum device simulation.

FPGA Accelerates Quantum Tensor Network Computing

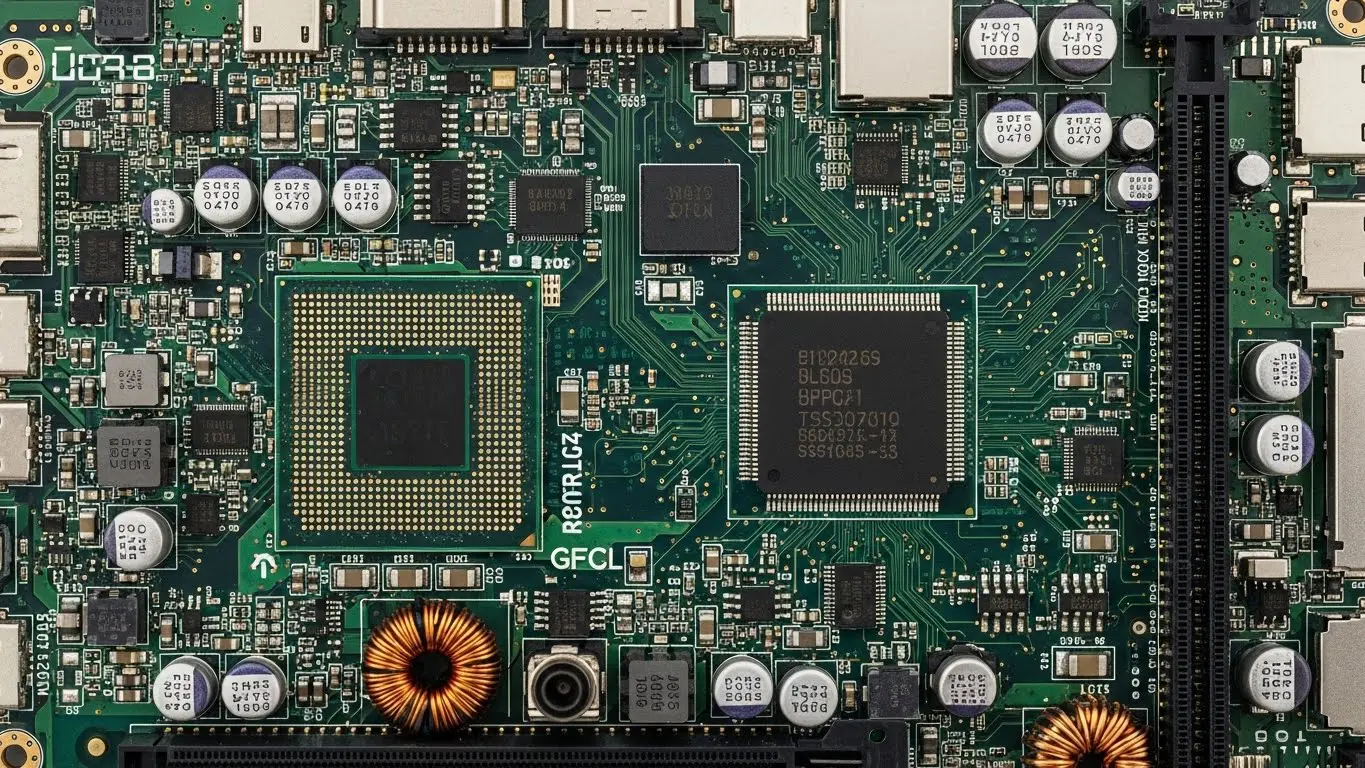

MicroCloud Hologram Inc. developed a system leveraging field programmable gate arrays (FPGA) to accelerate quantum tensor network computations, addressing limitations found in traditional CPU and GPU processing. The approach maps core computational modules—like tensor contraction and matrix multiplication—directly into FPGA hardware circuits. This allows for deep pipelined, high-density parallel computing, significantly reducing memory access and control overhead that typically hinder performance. HOLO’s technology utilizes a Hierarchical Tensor Contraction Pipeline with layers for input scheduling, core computing utilizing MAC Arrays, and output reduction. Through Verilog and high-level synthesis tools, tensor operation circuits are automatically generated and optimized for FPGA architecture.

Testing showed performance 1.7 times faster than CPUs, with over two times improved energy efficiency, demonstrating FPGA’s potential for quantum simulation and future quantum accelerators.

Tensor Network Algorithms & Quantum Spin Models

Tensor network (TN) algorithms efficiently address the exponential growth of data in quantum many-body systems by breaking down complex states into networks of smaller tensors. Models like matrix product states (MPS) and projected entangled pair states (PEPS) are fundamental to areas like condensed matter physics and quantum spin model simulations; however, increasing precision or entanglement rapidly increases computational demands. Specifically, expanding the entanglement rank from χ=8 to χ=32 can increase floating-point operations per iteration nearly a hundredfold, creating bottlenecks for traditional computing platforms. To overcome these limitations, MicroCloud Hologram Inc. Their Hierarchical Tensor Contraction Pipeline features layers for input/scheduling, core computing (using MAC Arrays), and output/reduction—all designed for parallel processing.

Hierarchical Tensor Contraction Pipeline Architecture

MicroCloud Hologram Inc.’s Hierarchical Tensor Contraction Pipeline is structured across three distinct levels to optimize tensor network computations. The input and scheduling layer first breaks down large tensors into smaller, manageable blocks, then analyzes data dependencies for efficient processing. A core computing layer, built with multiple MAC Arrays, performs tensor contractions of varying dimensions using custom logic for pipelined, parallel floating-point operations. Following computation, an output and reduction layer merges and normalizes tensor results, caching intermediate states for subsequent iterations. This pipeline uses Verilog and high-level synthesis to automatically generate tensor operation circuits, employing multi-partition strategies for diverse tensor connectivity.

Static scheduling and data reuse maximize throughput within the FPGA’s limited logic resources, achieving a significant performance increase over traditional CPU methods.

7x Performance Gain & FPGA Quantum Potential

HOLO’s technology delivers a significant performance boost through FPGA implementation, exceeding CPU speeds by 1.7x. The resulting deep pipelined architecture enables high-density parallel computing crucial for complex quantum simulations. This approach achieved over 2x improvement in energy efficiency alongside the speed increase, showcasing FPGA’s potential for quantum research. By reconstructing algorithms and employing Verilog and high-level synthesis tools, HOLO created a scalable, on-chip parallel array maximizing throughput. The company anticipates further expanding this technology to accelerate other quantum algorithms like VQE and QLSA, bridging classical and quantum computing.

It is believed that, through continuous research in this direction, FPGA will become an important bridge between quantum computing and classical computing, providing solid technical support for the industrialization development of quantum technology.

MicroCloud Hologram Inc.