The increasing prevalence of internet-connected devices creates significant challenges for data security and privacy, even when strong cryptographic algorithms are employed. Archisman Ghosh from Purdue University, along with co-authors, addresses the vulnerability of these systems to side-channel analysis (SCA) attacks, which exploit physical leaks like power consumption and electromagnetic radiation. This research presents novel, synthesizable circuit-level countermeasures designed to minimise performance overhead, a critical limitation of existing approaches for energy-constrained devices. The team achieves a zero-overhead integrated inductive technique capable of detecting both electromagnetic SCA and fault injection attacks, utilising a simple machine learning algorithm, and further contributes to the field by presenting a silicon-verified implementation of the Saber cryptographic algorithm, a finalist in the NIST post-quantum cryptography standardisation process, that achieves state-of-the-art energy efficiency and area usage.

Low-Overhead Countermeasures Against Side-Channel Attacks

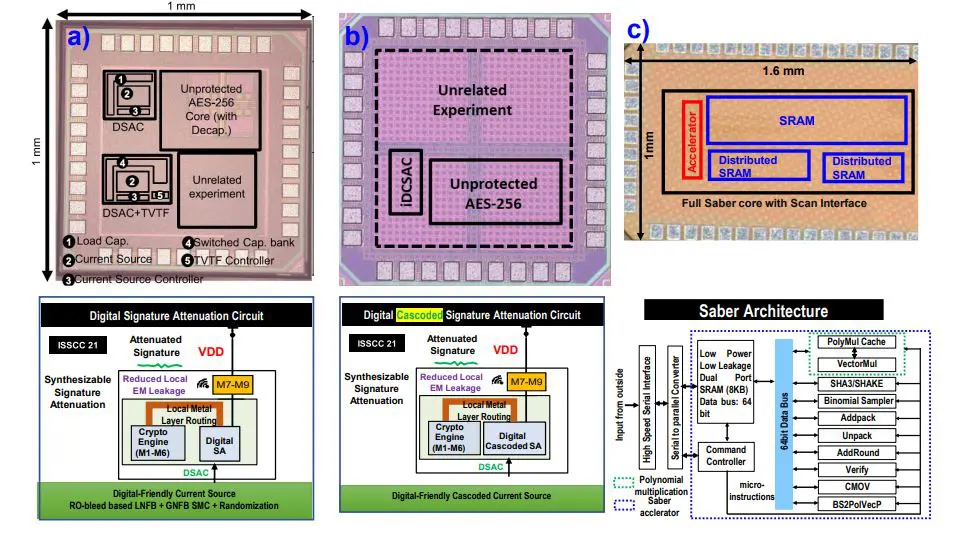

Researchers developed innovative circuit-level countermeasures to protect internet-connected devices against security breaches stemming from power consumption, electromagnetic radiation, and timing variations, collectively known as side-channel analysis (SCA) attacks. Recognizing that even mathematically secure cryptographic algorithms are vulnerable when implemented in hardware, the team focused on creating low-overhead solutions suitable for energy-constrained devices. Their work centers on a zero-overhead integrated inductive system capable of detecting both electromagnetic SCA and fault injection attacks, utilizing a simple machine learning algorithm for threat identification. To enhance security, the team engineered a novel digital signature attenuation circuit (DSAC) that achieves over 1.

25 billion Minimum Traces to Disclosure (MTD), a 25% improvement over existing methods and a 250-fold increase compared to single digital countermeasures. This attenuation is achieved through a synthesizable current source, strategically implemented with multi-stage ring oscillators as a bleed path to stabilize internal voltages and introduce randomization through power supply noise, reaching 20 million MTD independently. Further bolstering security, the team incorporated a time-varying transfer function (TVTF) at the power supply port, pushing the MTD beyond 1. 25 billion. The entire encryption engine is routed through local metal layers to minimize electromagnetic emanation, increasing resilience against EM SCA.

This solution was demonstrated in a 65nm test IC, showcasing its practicality for real-world applications. The team also pioneered a proactive approach to attack detection, embedding a single on-chip integrated loop around a cryptographic core. This loop functions as an on-chip H-field sensor, detecting voltage or clock glitching fault attacks and sensing approaching electromagnetic probes. The system can even induce electromagnetic noise to further enhance resilience. Measurements from a custom-built 65nm CMOS IC demonstrate the system’s ability to detect these attacks with nearly 100% accuracy after training with approximately 3000 traces. Researchers also developed a cascoded signature attenuation technique, achieving 200 million MTD through signature attenuation alone, and implemented a global switched-mode control loop to maintain stable current source operation, preventing attackers from exploiting potential vulnerabilities.

On-Chip Detection of Side-Channel and Fault Attacks

Researchers have developed a novel system capable of detecting electromagnetic and power side-channel attacks, as well as clock and voltage glitch-based fault injection attacks, with zero overhead using a machine learning algorithm. This integrated system, demonstrated using a 65nm CMOS IC, acts as an on-chip H-field sensor, identifying approaching electromagnetic probes and detecting voltage/clock glitching, while also inducing electromagnetic noise to enhance resilience against attacks. Experiments reveal the system achieves nearly 100% accuracy in detecting these attacks after training with approximately 3000 traces from the on-chip sensor. Further work focused on a sustainable signature attenuation technique, achieving 200 million masked traces (MTD) through digital-friendly current source attenuation.

To counter potential vulnerabilities, an intelligent attack detector was implemented, monitoring voltage at both the supply and AES nodes using ring oscillators. This detector identifies sudden voltage drops, signaling a potential attack within 0. 8ms, effectively preventing a correlated power analysis (CPA) attack. Significant progress was also made in post-quantum cryptography, culminating in the first silicon-verified Saber accelerator, a finalist in the NIST standardization procedure. This accelerator utilizes a memory-efficient striding Toom-Cook multiplier with lazy interpolation, resulting in a highly compact and low-power implementation.

The design achieves 38% less power consumption, four times less memory usage, a 36. 8% reduction in multiplier energy, and a 118-fold reduction in active power compared to state-of-the-art Saber accelerators. The accelerator occupies an active area of only 0. 158mm², the lowest reported to date, despite process disadvantages. These advancements demonstrate a substantial reduction in resource requirements for secure post-quantum cryptographic implementations.

Zero Overhead Attack Detection in Silicon

This research presents significant advances in protecting cryptographic systems against increasingly sophisticated side-channel and fault injection attacks, critical for securing internet-connected devices. Scientists have developed novel circuit-level countermeasures that demonstrate resilience against both power and electromagnetic analysis, as well as various fault injection techniques. A key achievement is the creation of an integrated inductive approach that detects these attacks with zero overhead, a substantial improvement over existing methods which often compromise energy efficiency. This allows for practical implementation in energy-constrained IoT devices where performance is paramount.

Furthermore, researchers successfully designed and verified a silicon implementation of Saber, a leading post-quantum cryptographic algorithm, achieving the lowest reported energy consumption and area amongst candidate designs. This contributes directly to the ongoing standardization process for post-quantum cryptography, ensuring future security against potential attacks from quantum computers. The team also explored techniques for detecting attacks on the countermeasures themselves, enhancing overall system robustness. While acknowledging that the effectiveness of any countermeasure is limited by the evolving landscape of potential attacks, this work establishes a strong foundation for future research into adaptable and resilient cryptographic hardware. Future investigations will likely focus on refining these techniques and exploring their application to a wider range of cryptographic algorithms and hardware platforms.

🗞 Extended Abstract: Synthesizable Low-overhead Circuit-level Countermeasures and Pro-Active Detection Techniques for Power and EM SCA

🧠 ArXiv: https://arxiv.org/abs/2512.00635