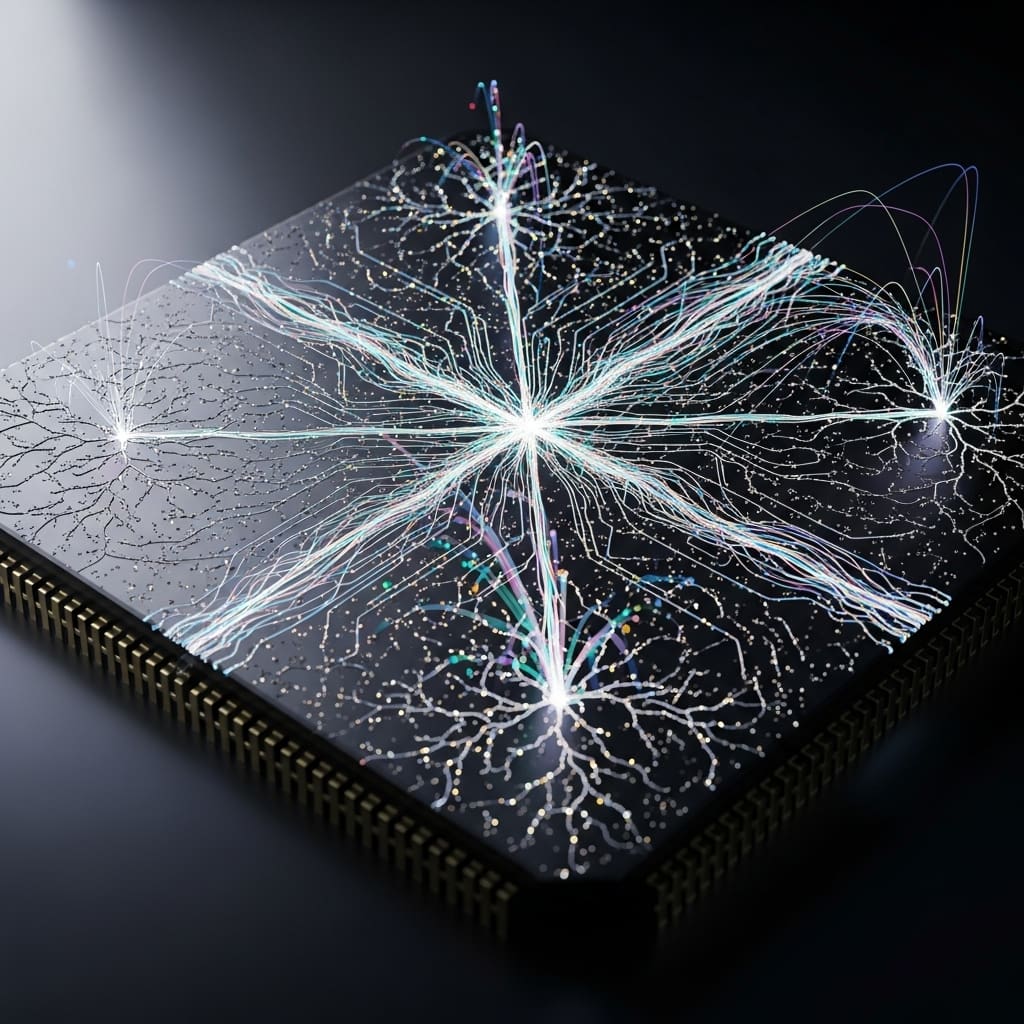

Neuromorphic computing represents a promising paradigm shift, offering the potential to accelerate and optimise a diverse range of computational kernels through its asynchronous, memory-centric architecture. However, a significant obstacle to progress lies in the absence of accurate and easily interpretable performance models for emerging neuromorphic hardware. Jonathan Timcheck, Alessandro Pierro, and Sumit Bam Shrestha, from Intel Corporation and LMU Munich, address this challenge with a novel runtime model specifically designed for Intel’s Loihi 2 chip. Their research introduces the first max-affine lower-bound model , a multi-dimensional roofline , that quantifies both compute and communication costs, crucial for understanding performance in spatially distributed systems. This model demonstrates a strong correlation with measured runtimes on Loihi 2, and provides analytical insights into scalability, ultimately empowering the development of faster algorithms and kernels for this innovative hardware platform.

A significant obstacle to progress, however, lies in the absence of accurate and easily interpretable performance models for emerging neuromorphic hardware. Their research introduces the first max-affine lower-bound model, a multi-dimensional roofline, that quantifies both compute and communication costs, crucial for understanding performance in spatially distributed systems.

Loihi 2 Performance Bottleneck Analysis and Modeling

The primary objective of this research is to address the lack of accurate and tractable performance models for neuromorphic systems. The approach centres on developing a runtime model capable of predicting performance on real neuromorphic hardware, with a particular emphasis on modelling communication time within the Network-on-Chip. As breaking the memory bandwidth wall of conventional von-Neumann architectures is a primary neuromorphic advantage, modelling communication time is especially important, though difficult due to complex congestion patterns in a heavily-loaded Network-on-Chip. The resulting max-affine lower-bound runtime model provides a multi-dimensional roofline, offering a means to evaluate and optimise neuromorphic algorithms and kernels.

Loihi 2 Runtime Prediction via Max-Affine Model

Scientists have developed the first max-affine lower-bound runtime model, a multi-dimensional roofline model, specifically for Intel’s Loihi 2 chip, offering a significant advancement in predicting performance on neuromorphic hardware. The research team meticulously quantified both computation and communication costs, utilising a suite of microbenchmarks to calibrate the model and ensure its accuracy. Experiments revealed a strong correlation between the model’s estimated runtime and actual measured runtime on Loihi 2, achieving a Pearson correlation coefficient consistently greater than or equal to 0.97 for a neural network linear layer, specifically matrix-vector multiplication. The study focused on precisely measuring runtime performance, demonstrating the model’s ability to accurately predict execution time across diverse configurations.

Data shows the model successfully predicted runtime for a Quadratic Unconstrained Binary Optimisation solver, further validating its applicability to complex applications. Researchers derived analytical expressions for communication-bottlenecked runtime, enabling detailed study of the linear layer’s scalability and revealing an area-runtime tradeoff dependent on spatial workload configurations. This analysis uncovered linear to superlinear runtime scaling with layer size, influenced by various constant factors. Tests prove the model’s predictive power extends to sparse linear layers, which heavily stress the communication mesh of Loihi 2, across a range of spatial placement patterns.

Measurements confirm the model accurately accounts for complex congestion patterns arising within the Network-on-Chip, a critical factor in neuromorphic system performance. The breakthrough delivers a quantitative lower-bound on kernel runtime, distinguishing between compute-bound and memory-bandwidth-bound kernels, and providing a valuable tool for both algorithm and hardware designers. Scientists achieved a precise quantitative abstraction that facilitates exchange and innovation between hardware and algorithm experts, addressing a key challenge in neuromorphic computing. This work introduces a novel max-affine lower-bound runtime model, a multi-dimensional roofline model, specifically designed for Intel’s Loihi 2 chip.

The model quantitatively assesses both compute and communication costs, leveraging a suite of microbenchmarks to accurately capture performance characteristics. By accounting for the asynchronous nature of the architecture, the research establishes a foundation for predicting runtime and optimising algorithm design on this neuromorphic hardware. The findings demonstrate a strong correlation, a Pearson correlation coefficient of at least 0.97, between the model’s predictions and measured runtime for a neural network linear layer and a Quadratic Unconstrained Binary Optimisation solver. Analytical expressions derived for communication-bottlenecked runtime reveal a trade-off between area and runtime when scaling the linear layer, highlighting the impact of spatial workload configurations on performance.

The authors acknowledge limitations inherent in a lower-bound model, noting that real-world performance may be influenced by factors not fully captured within the framework. Future research directions include exploring the model’s applicability to a wider range of algorithms and applications on Loihi 2, as well as investigating methods to refine the model’s accuracy by incorporating additional hardware-specific details. This work contributes a valuable tool for researchers and developers seeking to maximise the speed and efficiency of kernels on Loihi 2, offering insights into the interplay between computation, communication, and scalability within the neuromorphic system.

👉 More information

🗞 A Compute and Communication Runtime Model for Loihi 2

🧠 ArXiv: https://arxiv.org/abs/2601.10035