The development of energy-efficient hardware is crucial for realising the potential of neuromorphic computing, a paradigm inspired by the structure and function of the human brain. These systems rely on circuits that mimic neuronal behaviour, and a fundamental component is the winner-take-all (WTA) circuit, which selects the neuron with the strongest signal. Abdullah M. Zyarah from the University of Baghdad, Dhireesha Kudithipudi from the University of Texas at San Antonio, and colleagues present a novel WTA circuit design in their article, ‘Voltage Mode Winner-Take-All Circuit for Neuromorphic Systems’. Their research details a circuit, simulated using a 65nm process node, that achieves both k-winner functionality – selecting the k strongest inputs – and hysteresis, enhancing stability, while dissipating 34.9 microwatts of power and exhibiting a latency of 10.4 nanoseconds when processing 1000 inputs. The circuit’s utility is demonstrated through applications in spatial filtering and classification.

Neuromorphic computing represents a fundamental shift in information processing, moving away from the traditional von Neumann architecture towards systems inspired by the biological brain. These systems aim to replicate the efficiency and adaptability of biological neural networks, offering potential advantages in power consumption and processing speed, particularly for complex pattern recognition and real-time data analysis. A critical component enabling these capabilities is the winner-take-all (WTA) circuit, which facilitates competitive learning and efficient information selection, forming the basis for advanced neuromorphic architectures.

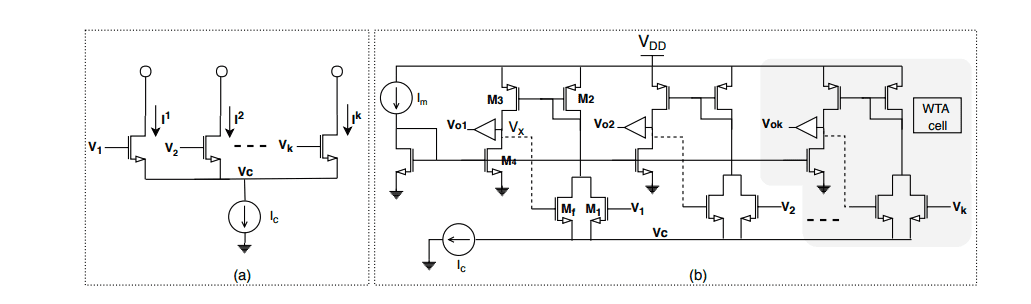

WTA circuits function by selecting the neuron with the strongest input signal from a group of competing neurons, effectively suppressing the activity of others and enabling efficient feature extraction and classification. Applications span image processing, rank modulation coding, vector quantization, and analog classification, demonstrating the circuit’s versatility across diverse computational tasks. Historically, both analog and digital implementations have been explored, each with inherent trade-offs in terms of power consumption, precision, and scalability, driving ongoing research into hybrid approaches. Analog WTA circuits generally offer lower power consumption and greater compactness, making them suitable for resource-constrained platforms, while digital implementations provide greater stability and precision but often require more complex circuitry and consume more power.

This work presents a novel voltage-mode WTA circuit designed for neuromorphic applications, prioritising high speed and low energy consumption. Simulation results, utilising a 65nm process node, demonstrate the circuit’s performance with 1000 inputs, highlighting its potential for spatial filtering and classification tasks, and enabling the creation of larger networks with increased computational power and adaptability. The design prioritises scalability and modularity, and operates using voltage signals, simplifying implementation and potentially reducing energy demands compared to current-mode circuits, and allowing for more straightforward integration with other analog and digital components within a larger neuromorphic system.

The circuit incorporates configurable properties, allowing it to function as a k-winner circuit – selecting the k largest inputs – and exhibits hysteresis, a characteristic that enhances stability and noise immunity, broadening its applicability within diverse neuromorphic architectures. To rigorously assess the circuit’s robustness, the team conducted corner analysis, evaluating performance under worst-case operating conditions, such as variations in temperature and supply voltage. This analysis provides confidence in the circuit’s reliability across a range of real-world scenarios, and validates its suitability for deployment in challenging environments. The circuit’s utility is further demonstrated through applications in spatial filtering, where it effectively identifies and enhances specific features within an image, and classification tasks, where it accurately categorises input data.

The design was simulated using a 65-nanometer technology node, ensuring compatibility with existing manufacturing infrastructure. Rigorous testing confirms the circuit’s robustness under varying operating conditions, and corner analysis systematically evaluates performance across process variations, voltage fluctuations, and temperature changes. The mean power consumption, measured at 40 microwatts with a standard deviation of 15.71 microwatts, indicates consistent performance across multiple simulations. Simulations demonstrate a mean latency of 10.4ns and a mean power dissipation of 40µW when processing 1000 inputs, with worst-case values of 17.61ns and 84.83µW respectively, indicating a robust and efficient design capable of handling substantial computational loads.

Researchers envision this circuit as a key building block for advanced neuromorphic chips, enabling the development of more efficient and powerful artificial intelligence systems, and addressing the growing demand for low-power, high-performance computing. By addressing the critical need for low-power, high-performance WTA circuits, this work contributes to the ongoing advancement of on-device learning and neuromorphic computing.

Future work focuses on integrating this WTA circuit into larger neuromorphic architectures, specifically spiking neural networks and hierarchical temporal memory (HTM) systems. Investigating the circuit’s performance within these complex systems will reveal its limitations and guide further optimisation. Exploring alternative circuit topologies and fabrication processes could potentially reduce power consumption and improve speed. Further research should also address the scalability of this design. While the current implementation demonstrates promising results with 1000 inputs, expanding the input capacity without compromising performance remains a significant challenge. Investigating methods for parallelising the circuit or employing more advanced fabrication techniques could facilitate this scalability. Implementing adaptive learning algorithms directly within the circuit could lead to more efficient and intelligent neuromorphic systems, paving the way for more adaptable and responsive computational architectures. This research demonstrates a significant step towards realising the full potential of neuromorphic computing, offering a pathway towards more efficient, intelligent, and adaptable computational systems.

👉 More information

🗞 Voltage Mode Winner-Take-All Circuit for Neuromorphic Systems

🧠 DOI: https://doi.org/10.48550/arXiv.2507.04338