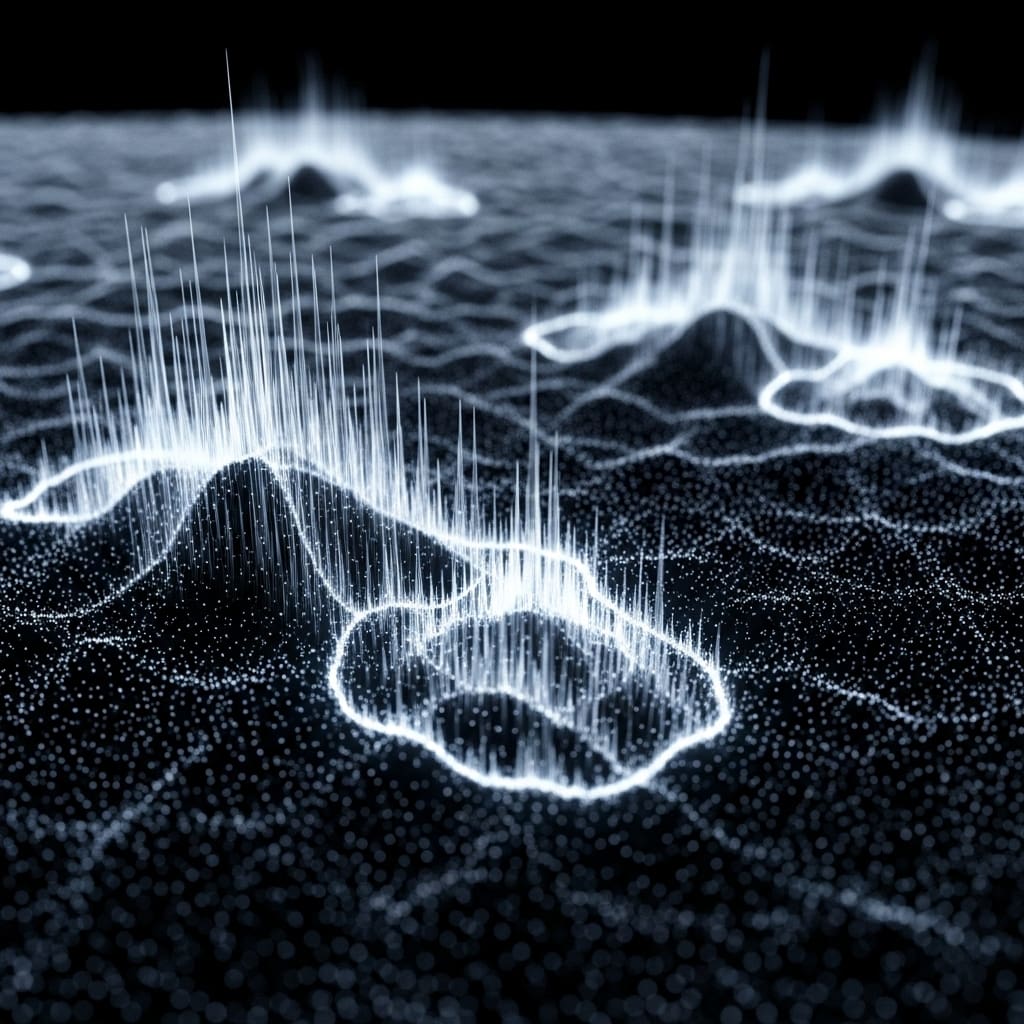

Researchers are increasingly exploring how the precise timing of spikes in neural networks can be harnessed for faster and more efficient computation. Natalila G Berloff, alongside colleagues, demonstrate a novel approach to address selection in these spiking networks, moving beyond traditional digitisation methods and embracing timing as a fundamental principle , a concept they term Polychronous Wave Computing (PWC). This work details PWC, a timing-native primitive that directly maps spike latencies to output routes using wave-domain processing and a programmable multiport interferometer, offering a potentially transformative pathway towards low-latency, energy-efficient artificial intelligence hardware across various platforms like photonics and oscillators. By deriving an operating envelope and demonstrating improved routing fidelity through nonlinear competition and phase tuning, this research establishes PWC as a promising coprocessor for spiking networks and sparse top-1 gates, paving the way for significant advances in neuromorphic computing.

The research team achieved this by phase-encoding spike times in a rotating frame and processing them with a programmable multiport interferometer, capable of evaluating K template correlations simultaneously. A subsequent driven-dissipative winner-take-all stage then performs a physical argmax, emitting a one-hot output port and effectively completing the address selection process.

The study establishes a clear operating envelope dictated by phase wrapping and mutual coherence, and importantly, collapses timing jitter, static phase mismatch, and dephasing into a single, manageable effective phase-noise budget. This budget directly predicts boundary-first failures and, crucially, provides an intensity-only calibration target for enhanced system performance. Simulations demonstrate that incorporating nonlinear competition significantly improves routing fidelity when compared to noisy linear intensity readout, showcasing the power of this approach. Indeed, hardware-in-the-loop phase tuning successfully rescued a temporal-order gate, boosting its accuracy from 55.9% to an impressive 97.2% even under conditions of strong static mismatch.

This innovative PWC system functions as a fast routing coprocessor suitable for LUT-style spiking networks and sparse top-1 gates, such as those used in mixture-of-experts routing. The research highlights its compatibility across diverse platforms including polaritonic, photonic, and oscillator systems, broadening its potential applications. By moving the comparison step into the physical substrate and digitizing only after parallel scoring, PWC addresses a critical bottleneck in current neuromorphic and photonic systems, where serial conversion and reduction often dominate latency and energy consumption. Experiments show that the system’s robustness is governed by the separation between the winning output and its closest competitor, a winner, runner-up margin, suggesting a practical intensity-only calibration loop for compensating static offsets and drift0.9% to 97.2% even under substantial static. The team measured the performance of a programmable multiport interferometer evaluating K template correlations in parallel, followed by a winner-take-all stage to emit a one-hot output port.

Results demonstrate that the operating envelope of PWC is governed by phase wrapping and mutual coherence, with timing jitter, static phase mismatch, and dephasing collapsing into a single effective phase-noise budget. Data shows this budget predicts boundary-first failures and provides an intensity-only calibration target for optimal performance. Simulations confirmed that nonlinear competition significantly improves routing fidelity compared to noisy linear intensity readout, enhancing the accuracy of the system. Tests prove that hardware-in-the-loop phase tuning rescued a temporal-order gate from 55.9% to 97.2% accuracy under strong static mismatch, a remarkable improvement in signal processing.

Measurements confirm that the device-predicted routing error, denoted as proute, varies with normalized timing jitter (σt/Twrap) and static phase disorder (σθ). The research team observed that for several static phase-disorder levels, the relationship between proute and σt/Twrap could be accurately predicted and read off directly from device noise budgets to task-level accuracy. Specifically, analytical results derived in Appendix A detail the linear interferometric score for output/template k, expressed as Ψk = N X j=1 |Jjk| exp[i (θjk −Ωtj)], where tj represents input times and Ω is the angular rate. The study further quantified the coherent-to-incoherent intensity ratio (Ck) as a measure of weight robustness, finding that 1 ≤ Ck ≤ N, with Ck = N for uniform magnitudes. Analysis of phase noise, incorporating jitter, static offsets, and finite coherence, revealed that the effective phase error variance (σ2 eff) is the sum of variances from timing jitter, static offsets, and coherence loss: σ2 eff ≡σ2 φ + σ2 θ + σ2 coh. The system utilises a programmable multiport interferometer to evaluate template correlations in parallel, followed by a winner-take-all stage to select the most appropriate output. Researchers demonstrated that PWC can effectively address challenges posed by phase wrapping, mutual coherence, and timing jitter, consolidating these factors into a single, manageable phase-noise budget.

Simulations revealed that nonlinear competition enhances routing accuracy compared to linear intensity readout, and hardware-in-the-loop phase tuning significantly improved the performance of a temporal-order gate, increasing its accuracy from 55.9% to 97.2% even under substantial static mismatch. This suggests PWC could function as a fast routing coprocessor for various spiking network architectures and sparse top-1 gates across different technological platforms, including polaritonic, photonic, and oscillator systems. The authors acknowledge that the system’s performance is influenced by the effective phase variance and that the runner-up signal can grow with increasing template library size. They highlight the importance of calibration to mitigate fabrication offsets and drift, ensuring reliable address mapping. Future work could focus on optimising the calibration procedure and exploring the scalability of PWC to larger and more complex spiking networks. These findings represent a significant step towards realising truly timing-native computation, potentially unlocking new possibilities for low-power, high-speed neuromorphic computing.

👉 More information

🗞 Polychronous Wave Computing: Timing-Native Address Selection in Spiking Networks

🧠 ArXiv: https://arxiv.org/abs/2601.13079