Researchers are tackling a central challenge in quantum computing, scaling up qubit numbers while maintaining performance. Oscar W. Kennedy, Waqas Ahmad, and Robert Armstrong, all from Oxford Quantum Circuits, alongside colleagues from Oxford Quantum Circuits, detail a novel wafer-scale packaging architecture capable of housing over 500 superconducting qubits on a single 3-inch die. This work is significant because it demonstrates a pathway towards building larger, more complex quantum processors and enabling the high-throughput testing crucial for optimising qubit fabrication. The team engineered the package to minimise signal interference, material loss, and thermal stress, allowing robust operation at extremely low temperatures and compatibility with standard dilution refrigerators. Measurements confirm median coherence times and high readout fidelity across a substantial number of qubits, validating the package’s ability to support large-scale integration without sacrificing device quality and offering a powerful tool for characterising and improving qubit performance.

This new package design addresses critical challenges in building larger quantum processors, specifically mitigating signal interference and managing heat dissipation at extremely low temperatures.

The research demonstrates that large-scale qubit integration does not necessarily compromise individual qubit performance, a crucial finding for future quantum computer development. By suppressing unwanted radio frequency signals and carefully controlling thermal contraction, the package maintains the delicate quantum states necessary for computation.

The package is constructed with multiple layers, including a printed circuit board, aluminium spacer, and the qubit-populated wafer, meticulously assembled and sealed to create a shielded and thermally stable environment. System-level heat-load calculations confirm the package’s compatibility with standard commercial dilution refrigerators, essential for maintaining the millikelvin temperatures required for superconductivity.

Measurements performed on qubits within the package reveal median T1 and T2e coherence times around 100 microseconds for approximately 100 qubits, alongside a median readout fidelity of 97.5% across 54 qubits and a median qubit temperature of 36 millikelvin. These results not only validate the package’s performance but also highlight its potential as a high-throughput testing platform.

The ability to measure a large number of qubits simultaneously allows researchers to identify performance variations and optimise fabrication processes with unprecedented efficiency. This statistical feedback loop is critical for improving qubit quality and reducing errors, paving the way for the creation of more reliable and powerful quantum processors. The design considers common problems across various solid-state qubit systems, suggesting broader applicability beyond the specific coaxmon qubits used in this study.

High-fidelity qubit performance and coherence limitations within a packaged superconducting circuit

Measurements across over 100 qubits reveal median T1 and T2e coherence times of approximately 100 microseconds. This performance signifies robust qubit behaviour within the newly developed package, demonstrating minimal disruption to fundamental quantum properties. Readout fidelity, assessed on 54 qubits, achieved a median value of 97.5%, corresponding to median readout errors of 2.5%.

This high level of accuracy in state determination is crucial for reliable quantum computation and control. Furthermore, the study established a median qubit temperature of 36 millikelvin across the same 54 qubits, indicating efficient cooling and thermal stability within the packaged system. Analysis of the coherence data, obtained from a large sample size, demonstrates that the observed coherence limits are primarily dictated by the material properties of the qubit wafer itself.

Bootstrap analysis of the coherence dataset confirms low error margins in determining median coherence times from smaller qubit populations. However, accurately defining the minimum coherence times, a critical parameter for large-scale quantum computers, necessitates measurements from a substantial number of qubits. System-level heat-load calculations indicate the package is compatible with operation in standard commercial dilution refrigerators, easing integration into existing quantum computing infrastructure.

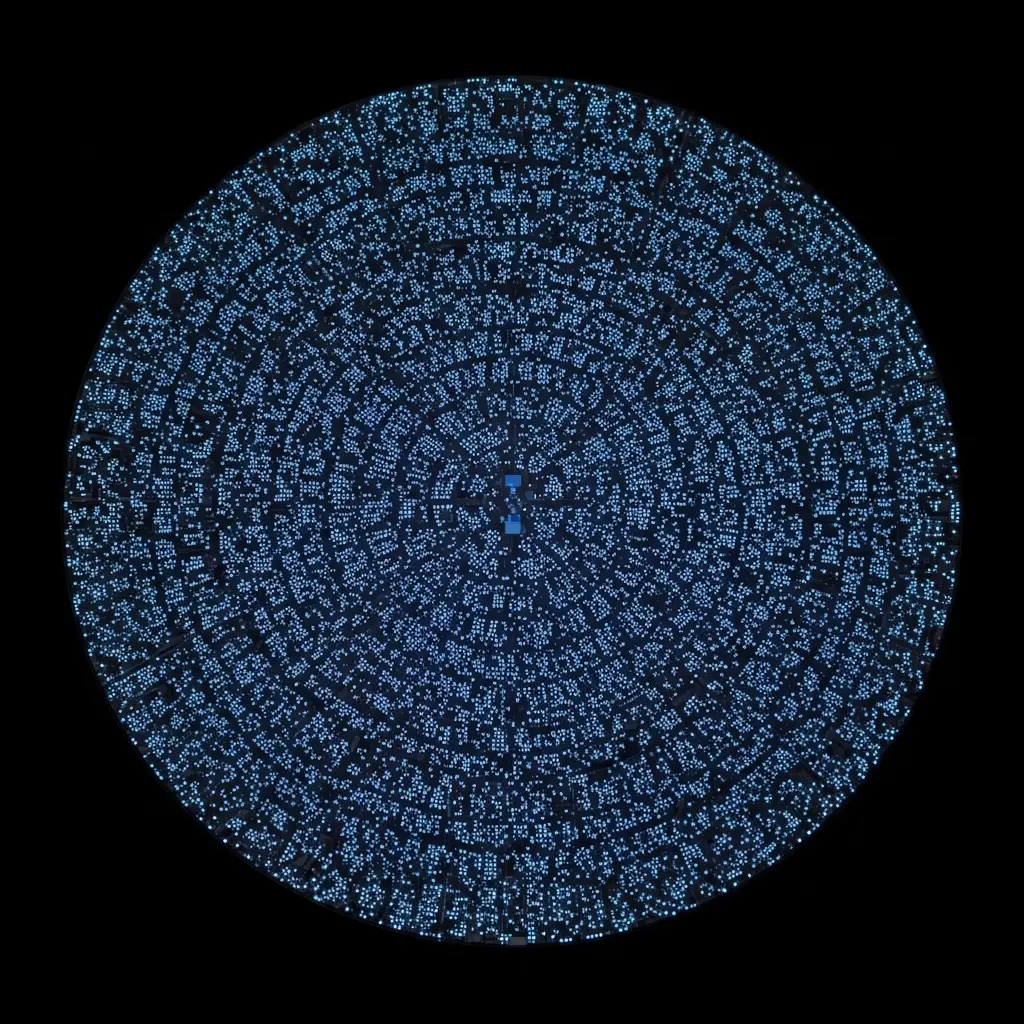

The package architecture supports over 500 qubits fabricated on a single 3-inch die, enabling wafer-scale integration without compromising device performance. The design incorporates features to suppress parasitic RF modes and mitigate material loss through simulation-informed engineering. Differential thermal contraction, a common challenge in cryogenic systems, is actively managed to ensure robust operation at millikelvin temperatures. This package design, omitting per-qubit control lines and instead utilising multiplexed readout, facilitates high-throughput measurements and provides a rich statistical dataset for optimising qubit design and manufacture.

Cryogenic packaging design for large-scale superconducting qubit arrays

A wafer-scale packaging architecture, supporting over 500 superconducting qubits on a single 3-inch die, underpins this work. This package was meticulously engineered to suppress parasitic radio frequency (RF) modes, which can introduce noise and decoherence, and to mitigate material loss through simulation-informed design. Crucially, the design also addresses differential thermal contraction, the varying expansion and contraction of materials at cryogenic temperatures, to ensure robust operation at millikelvin temperatures.

System-level heat-load calculations were performed to confirm compatibility with commercial dilution refrigerators, essential for maintaining the extremely low temperatures required for qubit operation. The research team modelled the thermal performance of a fully-wired package, accounting for 504 attenuated drive lines, 56 readout configurations, and 56 attenuated lines for parametric amplifier pumps.

These calculations considered both passive heat load from wiring and dissipative heating from microwave control and readout signals. Conservative estimates of effective continuous drive power, ranging from -64 dBm in a high-throughput configuration to -78 dBm with drive lines included, were used, alongside a typical pump power of approximately -60 dBm per parametric amplifier.

Simulations demonstrated that the package could operate within the limits of commercially available dilution refrigerators, with a maximum predicted heat load of around 3 μW. Characterisation of the packaged qubits began with measurements performed on 105 available qubits across 12 multiplexing cells. QBlox control hardware, utilising three QCM-RF II cards for qubit control and six QRM-RF cards for readout, enabled simultaneous addressing of six lines.

Control and readout signals were coupled at room temperature using directional couplers and routed to multiplexing elements on the printed circuit board (PCB). A streamlined, automated calibration routine was implemented to spectroscopically identify qubit and resonator frequencies, optimise pulse parameters, and measure coherence times (T1, T2e, T2*), accelerating the characterisation of a large qubit array. This routine leveraged the 9-to-1 multiplexing architecture, processing qubits in batches to reduce the overall calibration time.

The Bigger Picture

Scientists building quantum computers have long grappled with a fundamental bottleneck: scaling up from a handful of qubits to the thousands, even millions, needed for genuinely useful computation. It isn’t simply about making more qubits, but about maintaining their delicate quantum states, their coherence, as the system grows more complex. This work represents a significant step towards overcoming that challenge, demonstrating a packaging architecture capable of housing and operating over 500 qubits on a single chip without substantial performance degradation.

For years, the engineering has lagged the physics; theoretical advances in qubit design outstripped our ability to connect, control, and cool them effectively. The demonstrated architecture tackles several critical issues simultaneously, suppressing unwanted radio frequency interference, managing heat dissipation, and accommodating the differing thermal contractions of materials at cryogenic temperatures.

Crucially, it appears compatible with existing dilution refrigerator technology, avoiding the need for entirely new and expensive infrastructure. However, maintaining high fidelity across such a large array remains a considerable undertaking. While median coherence and readout fidelities are encouraging, the distribution of performance will inevitably be uneven.

Identifying and mitigating those “outlier” qubits, those that quickly lose coherence, will be essential for building reliable processors. Furthermore, this packaging solution is specific to superconducting qubits; other qubit modalities may require radically different approaches. Looking ahead, this advance should accelerate the development of larger, more complex quantum processors.

We can anticipate a shift towards more automated, high-throughput testing of qubit devices, allowing manufacturers to rapidly identify and correct fabrication flaws. Beyond quantum computing, this wafer-scale packaging technology could find applications in other areas of sensitive microwave electronics, such as advanced sensors and astronomical receivers, where minimising signal loss and maintaining precise control are paramount.

🗞 Design and Operation of Wafer-Scale Packages Containing >500 Superconducting Qubits

🧠 ArXiv: https://arxiv.org/abs/2602.12773