Quantum circuits, essential for modern applications like advanced algorithms and quantum adders, often suffer from inefficiencies after compilation, manifesting as excessive numbers of operations or lengthy circuit depths which ultimately reduce performance. To address this challenge, Xinpeng Li, Ji Liu, and Shuai Xu, alongside Paul Hovland from Argonne National Laboratory and Vipin Chaudhary from Case Western Reserve University, present HOPPS, a novel algorithm that optimises circuits composed of fundamental building blocks. HOPPS achieves this by intelligently synthesising phase polynomials, generating circuits with significantly reduced operational counts and depths, and importantly, the team introduces a blockwise optimisation strategy to improve scalability for larger, more complex circuits. Empirical results demonstrate that HOPPS outperforms existing optimisation tools, reducing CNOT counts by up to 50% and depths by up to 57%, and even achieves substantial reductions in larger circuits after mapping with Qiskit, representing a significant step towards more efficient and reliable quantum computation.

After compilation, many of these circuits often contain a large number of CNOT gates or exhibit significant depth, which can reduce the overall fidelity of the computation. Consequently, researchers have introduced HOPPS, a SAT-based algorithm that generates CNOT and Rz blocks with optimized CNOT count or depth, directly addressing limitations of near-term quantum devices where two-qubit gates are prone to errors and have longer durations. While HOPPS’s pursuit of optimality proves beneficial, the team focused on improving the algorithm’s scalability while maintaining its ability to generate high-fidelity quantum circuits.

Quantum Circuit Synthesis and Optimization Landscape

A comprehensive review of current research reveals a vibrant and rapidly evolving field dedicated to optimizing quantum circuits. Numerous studies focus on reducing circuit complexity by minimizing the number of gates, particularly non-Clifford gates, or reducing the overall circuit depth. Researchers are also exploring methods for representing and optimizing circuits using phase polynomial synthesis algorithms and leveraging architecture-aware synthesis techniques. Several studies investigate depth-optimal quantum layout synthesis, often employing SAT solvers to achieve efficient results. Machine learning approaches, such as AlphaTensor, are also emerging as promising tools for discovering better circuit decompositions.

A key challenge lies in mapping logical quantum circuits onto the physical connectivity of quantum processors, requiring minimization of SWAP gates to move qubits around. Researchers are developing optimal layout synthesis techniques and employing SAT solving to address this problem. Synthesis approaches focus on creating quantum circuits from higher-level descriptions, such as Hamiltonians, and tools like the Berkeley Quantum Synthesis Toolkit are automating the compilation process. Applications and benchmarks, including the Quantum Approximate Optimization Algorithm, are used to test and validate optimization techniques. Recent trends highlight the increased use of SAT/SMT solvers, the application of machine learning, and a strong emphasis on scalability and architecture awareness. Overall, the field is characterized by a diverse range of techniques and a growing focus on practical implementation and real-world hardware constraints.

HOPPS Optimizes Quantum Circuit Gate Counts

Scientists have developed a new method for optimizing quantum circuits composed of CNOT and Rz gates, crucial components in many quantum algorithms. This work introduces HOPPS, a SAT-based algorithm that generates circuits with minimized CNOT gate counts or depths, directly addressing a key limitation of near-term quantum devices. The team’s approach leverages the phase polynomial representation of quantum circuits, enabling efficient synthesis and verification, and scales linearly with the number of qubits. Experiments demonstrate that HOPPS, when used as a peephole optimizer, reduces the number of CNOT gates by up to 50.

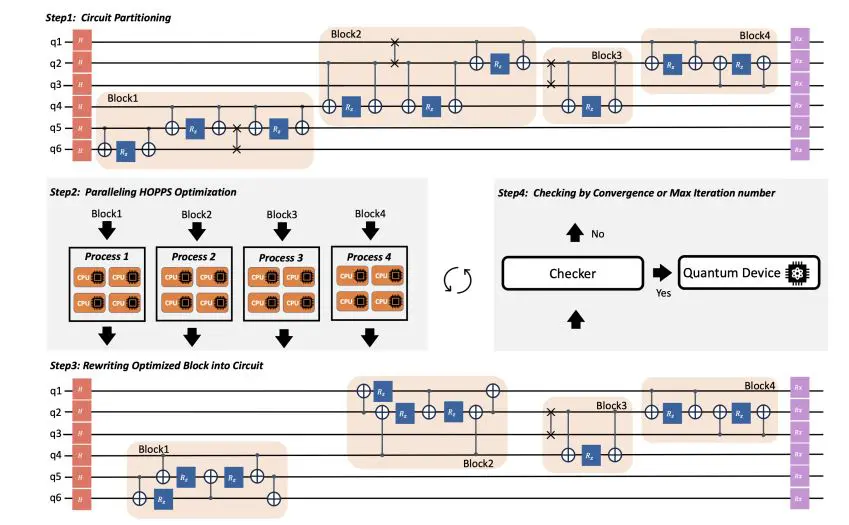

0% and the CNOT depth by up to 57. 1% under specific optimization conditions. For larger circuits, after mapping to realistic quantum hardware, the iterative blockwise optimization strategy, combined with HOPPS, achieves reductions in both CNOT count and depth, reaching up to 44. 4% and 42. 4% respectively. This iterative approach partitions large circuits into smaller, manageable blocks, optimizes each block individually, and repeats the process, enabling efficient parallel execution. The team’s results confirm that HOPPS can generate circuits that are doubly optimal, minimizing both CNOT count and depth simultaneously, potentially enabling more complex quantum algorithms to be executed with improved fidelity and reduced error rates.

Hardware-Aware Quantum Circuit Optimisation with HOPPS

The research team developed a novel approach to quantum circuit synthesis, named HOPPS, which efficiently generates circuits composed of CNOT and Rz gates. This method addresses a key challenge in quantum computing, namely minimizing the number of CNOT gates and the circuit depth, both of which directly impact the fidelity of quantum computations. HOPPS achieves this through a hardware-aware optimization process that seeks the most efficient arrangement of these fundamental gates. To further enhance its capabilities with larger, more complex circuits, the team introduced an iterative blockwise optimization strategy.

This involves partitioning a large circuit into smaller blocks, optimizing each block individually with HOPPS, and then repeating this process multiple times. Empirical results demonstrate that this iterative approach significantly reduces both CNOT count and circuit depth, surpassing the performance of existing near-optimal synthesis tools and even improving upon previously established methods. Specifically, reductions of up to 50. 0% in CNOT count and 57. 1% in CNOT depth were observed using this technique. Comparisons with the QSearch synthesizer revealed that HOPPS not only achieves comparable synthesis quality, identical CNOT counts and depths, but also requires less execution time, demonstrating improved scalability. Future work will likely focus on extending the scalability of HOPPS to even larger circuits and exploring its application to a wider range of quantum algorithms and hardware platforms.

🗞 HOPPS: Hardware-Aware Optimal Phase Polynomial Synthesis with Blockwise Optimization for Quantum Circuits

🧠 ArXiv: https://arxiv.org/abs/2511.18770