The increasing demand for artificial intelligence at the network edge requires innovative hardware solutions that minimise energy use and processing delays, particularly when dealing with time-varying data. Yifan Wang, Muhammad Sakib Shahriar, Salma Soliman, and colleagues at various institutions demonstrate a significant advance in this field with a novel transistor design incorporating both fast, temporary memory and slower, persistent storage within a single device. This ferroelectric transistor, built from hafnium-zirconium-oxide and silicon, achieves dual-memory operation by cleverly combining the properties of ferroelectric polarisation for long-term storage with engineered channel-charge relaxation for short-term memory. The resulting system not only performs complex tasks with remarkable speed and energy efficiency, achieving a 1000-fold increase in response time and a substantial reduction in energy consumption, but also establishes a broadly applicable principle for designing future, energy-efficient hardware for edge computing and beyond.

FeFETs and Non-Quasi-Static Reservoir Computing

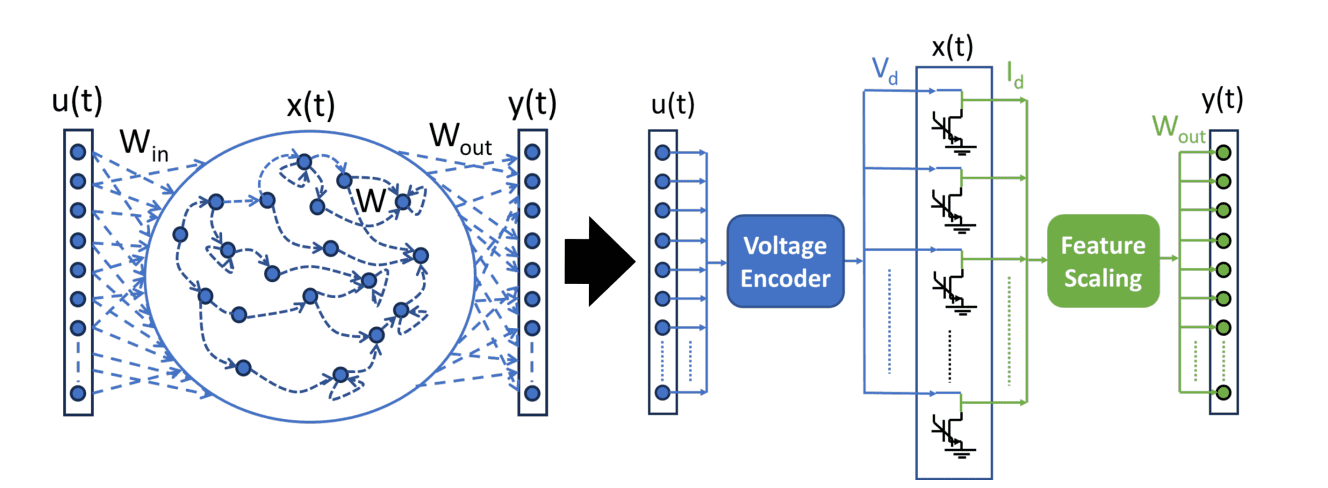

This research details the use of a charge-deficit Non-Quasi-Static (NQS) model to improve reservoir computing, specifically using Ferroelectric Field-Effect Transistors (FeFETs). Reservoir computing is a type of neural network that processes time-varying data, and FeFETs are attractive for this application due to their inherent non-linearity and dynamic behavior. Accurate modeling of these transistors is crucial, and this work addresses the limitations of traditional methods by employing NQS models that simulate dynamic charge trapping and release, significantly improving simulation accuracy and reservoir performance. The team utilizes an NQS model that accounts for charge deficit, providing a more accurate representation of the transistor’s transient response and capturing the interplay between charge trapping, hysteresis, and dynamic behavior. Simulations, performed using platforms like Ginestra, validate the model and allow researchers to optimize the reservoir computer design.

Ferroelectric Transistor Enables Dual Memory Computing

Scientists have achieved a breakthrough in physical reservoir computing by demonstrating a CMOS-compatible ferroelectric transistor that enables dual-memory operation, addressing limitations in energy consumption and latency for edge artificial intelligence. The device utilizes hafnium-zirconium-oxide and silicon to create both non-volatile long-term memory (LTM) from ferroelectric polarization and volatile short-term memory (STM) driven by engineered gate-source/drain overlap capacitance. This innovative design allows the ferroelectric state to deterministically control the NQS time constant and behavior, switching between paired-pulse facilitation and depression. The device achieves a 20 microsecond response time, a thousand-fold improvement over existing systems, and consumes 1.

5x 10^-7 Joules of energy, providing a pathway for immediately manufacturable, energy-efficient edge intelligence. Analysis of the device characteristics demonstrates pronounced anticlockwise hysteresis loops, confirming the existence of multi-level switchable polarization states and robust non-volatile LTM. The overlap capacitance enables a non-quasi-static (NQS) channel charge response, allowing for microsecond-scale dynamics essential for real-time edge computing. Measurements confirm that the dominant time constant scales with device geometry and dielectric stack engineering, enabling tuning of the dynamics. This co-engineering of ferroelectric and NQS charge dynamics establishes a scalable platform for physical reservoir computing.

Ferroelectric Memory Enables Efficient Edge Computing

This work successfully demonstrates a new CMOS-compatible platform integrating ferroelectric and semiconductor materials, achieving dual-memory operation essential for efficient edge computing. Researchers engineered a device utilizing hafnium-zirconium-oxide and silicon, creating both non-volatile long-term memory from ferroelectric polarization and volatile short-term memory through carefully designed channel-charge relaxation. This innovative approach allows deterministic control over the device’s behavior, switching between paired-pulse facilitation and depression, and effectively tuning the strength of the short-term memory. Beyond demonstrating successful reservoir computing, this research establishes key material-engineering principles for neuromorphic hardware, including dual-timescale functionality and material-parameter tunability. These principles extend beyond neuromorphic applications, potentially enabling tunable volatile memory using oxide semiconductors and opening avenues for adaptive analog circuits and reconfigurable sensors.

👉 More information

🗞 A Dual-Memory Ferroelectric Transistor Emulating Synaptic Metaplasticity for High-Speed Reservoir Computing

🧠 ArXiv: https://arxiv.org/abs/2511.07830